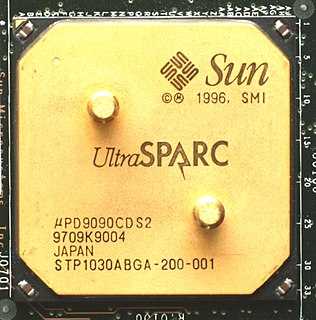

| Produced | From 1993 to 1996 |

|---|---|

| Designed by | Ross Technology |

| Max. CPU clock rate | 40 MHz to 200 MHz |

| Instruction set | SPARC V8 |

| Cores | 1 |

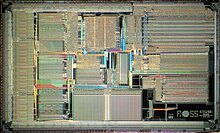

The hyperSPARC, code-named "Pinnacle", is a microprocessor that implements the SPARC Version 8 instruction set architecture (ISA) developed by Ross Technology for Cypress Semiconductor.

A microprocessor is a computer processor that incorporates the functions of a central processing unit on a single integrated circuit (IC), or at most a few integrated circuits. The microprocessor is a multipurpose, clock driven, register based, digital integrated circuit that accepts binary data as input, processes it according to instructions stored in its memory, and provides results as output. Microprocessors contain both combinational logic and sequential digital logic. Microprocessors operate on numbers and symbols represented in the binary number system.

SPARC is a reduced instruction set computing (RISC) instruction set architecture (ISA) originally developed by Sun Microsystems. Its design was strongly influenced by the experimental Berkeley RISC system developed in the early 1980s. First released in 1987, SPARC was one of the most successful early commercial RISC systems, and its success led to the introduction of similar RISC designs from a number of vendors through the 1980s and 90s.

An instruction set architecture (ISA) is an abstract model of a computer. It is also referred to as architecture or computer architecture. A realization of an ISA is called an implementation. An ISA permits multiple implementations that may vary in performance, physical size, and monetary cost ; because the ISA serves as the interface between software and hardware. Software that has been written for an ISA can run on different implementations of the same ISA. This has enabled binary compatibility between different generations of computers to be easily achieved, and the development of computer families. Both of these developments have helped to lower the cost of computers and to increase their applicability. For these reasons, the ISA is one of the most important abstractions in computing today.

Contents

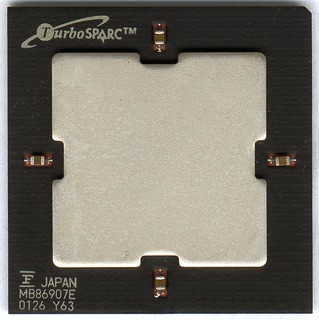

The hyperSPARC was introduced in 1993, and competed with the Sun Microsystems SuperSPARC. Raju Vegesna was the microarchitect. The hyperSPARC was Sun Microsystem's primary competitor in the mid-1990s. When Fujitsu acquired Ross from Cypress, the hyperSPARC was considered to be more important by its new owner than the SPARC64 developed by HAL Computer Systems, also a Fujitsu subsidiary, a view which was shared with analysts.

Sun Microsystems, Inc. was an American company that sold computers, computer components, software, and information technology services and created the Java programming language, the Solaris operating system, ZFS, the Network File System (NFS), and SPARC. Sun contributed significantly to the evolution of several key computing technologies, among them Unix, RISC processors, thin client computing, and virtualized computing. Sun was founded on February 24, 1982. At its height, the Sun headquarters were in Santa Clara, California, on the former west campus of the Agnews Developmental Center.

The SuperSPARC is a microprocessor that implements the SPARC V8 instruction set architecture (ISA) developed by Sun Microsystems. 33 and 40 MHz versions were introduced in 1992. The SuperSPARC contained 3.1 million transistors. It was fabricated by Texas Instruments (TI) at Miho, Japan in a 0.8 micrometre triple-metal BiCMOS process.

SPARC64 is a microprocessor developed by HAL Computer Systems and fabricated by Fujitsu. It implements the SPARC V9 instruction set architecture (ISA), the first microprocessor to do so. SPARC64 was HAL's first microprocessor and was the first in the SPARC64 brand. It operates at 101 and 118 MHz. The SPARC64 was used exclusively by Fujitsu in their systems; the first systems, the Fujitsu HALstation Model 330 and Model 350 workstations, were formally announced in September 1995 and were introduced in October 1995, two years late. It was succeeded by the SPARC64 II in 1996.