Alpha is a 64-bit reduced instruction set computer (RISC) instruction set architecture (ISA) developed by Digital Equipment Corporation (DEC). Alpha was designed to replace 32-bit VAX complex instruction set computers (CISC) and to be a highly competitive RISC processor for Unix workstations and similar markets.

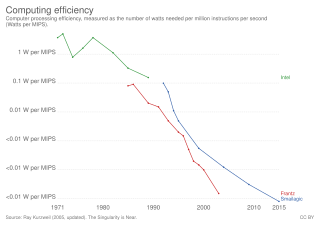

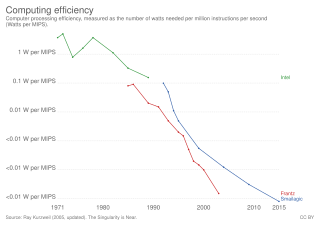

Instructions per second (IPS) is a measure of a computer's processor speed. For complex instruction set computers (CISCs), different instructions take different amounts of time, so the value measured depends on the instruction mix; even for comparing processors in the same family the IPS measurement can be problematic. Many reported IPS values have represented "peak" execution rates on artificial instruction sequences with few branches and no cache contention, whereas realistic workloads typically lead to significantly lower IPS values. Memory hierarchy also greatly affects processor performance, an issue barely considered in IPS calculations. Because of these problems, synthetic benchmarks such as Dhrystone are now generally used to estimate computer performance in commonly used applications, and raw IPS has fallen into disuse.

The StrongARM is a family of computer microprocessors developed by Digital Equipment Corporation and manufactured in the late 1990s which implemented the ARM v4 instruction set architecture. It was later acquired by Intel in 1997 from DEC's own Digital Semiconductor division as part of a settlement of a lawsuit between the two companies over patent infringement. Intel then continued to manufacture it before replacing it with the StrongARM-derived ARM-based follow-up architecture called XScale in the early 2000s.

VAX is a series of computers featuring a 32-bit instruction set architecture (ISA) and virtual memory that was developed and sold by Digital Equipment Corporation (DEC) in the late 20th century. The VAX-11/780, introduced October 25, 1977, was the first of a range of popular and influential computers implementing the VAX ISA. The VAX family was a huge success for DEC, with the last members arriving in the early 1990s. The VAX was succeeded by the DEC Alpha, which included several features from VAX machines to make porting from the VAX easier.

The VAXstation is a discontinued family of workstation computers developed and manufactured by Digital Equipment Corporation using processors implementing the VAX instruction set architecture. VAXstation systems were typically shipped with either the OpenVMS or ULTRIX operating systems. Many members of the VAXstation family had corresponding MicroVAX variants, which primarily differ by the lack of graphics hardware.

The CVAX is a microprocessor chipset developed and fabricated by Digital Equipment Corporation (DEC) that implemented the VAX instruction set architecture (ISA). The chipset consisted of the CVAX 78034 CPU, CFPA floating-point accelerator, CVAX clock chip, and the associated support chips, the CVAX System Support Chip (CSSC), CVAX Memory Controller (CMCTL), and CVAX Q-Bus Interface Chip (CQBIC).

The MicroVAX is a discontinued family of low-cost minicomputers developed and manufactured by Digital Equipment Corporation (DEC). The first model, the MicroVAX I, was first shipped in 1984. They used processors that implemented the VAX instruction set architecture (ISA) and were succeeded by the VAX 4000. Many members of the MicroVAX family had corresponding VAXstation variants, which primarily differ by the addition of graphics hardware. The MicroVAX family supports Digital's VMS, ULTRIX and VAXELN operating systems. Prior to VMS V5.0, MicroVAX hardware required a dedicated version of VMS named MicroVMS.

The PowerPC 600 family was the first family of PowerPC processors built. They were designed at the Somerset facility in Austin, Texas, jointly funded and staffed by engineers from IBM and Motorola as a part of the AIM alliance. Somerset was opened in 1992 and its goal was to make the first PowerPC processor and then keep designing general purpose PowerPC processors for personal computers. The first incarnation became the PowerPC 601 in 1993, and the second generation soon followed with the PowerPC 603, PowerPC 604 and the 64-bit PowerPC 620.

The DEC 4000 AXP is a series of departmental server computers developed and manufactured by Digital Equipment Corporation introduced on 10 November 1992. These systems formed part of the first generation of systems based on the 64-bit Alpha AXP architecture, and at the time of introduction, ran Digital's OpenVMS AXP or OSF/1 AXP operating systems.

The V-11, code-named "Scorpio", is a miniprocessor chip set implementation of the VAX instruction set architecture (ISA) developed and fabricated by Digital Equipment Corporation (DEC).

The DEC 7000 AXP and DEC 10000 AXP are a series of high-end multiprocessor server computers developed and manufactured by Digital Equipment Corporation, introduced on 10 November 1992. These systems formed part of the first generation of systems based on the 64-bit Alpha AXP architecture and at the time of introduction, ran Digital's OpenVMS AXP operating system, with DEC OSF/1 AXP available in March 1993. They were designed in parallel with the VAX 7000 and VAX 10000 minicomputers, and are identical except for the processor module(s) and supported bus interfaces. A field upgrade from a VAX 7000/10000 to a DEC 7000/10000 AXP was possible by means of swapping the processor boards.

The VAX 4000 is a discontinued family of low-end minicomputers developed and manufactured by Digital Equipment Corporation using microprocessors implementing the VAX instruction set architecture (ISA). The VAX 4000 succeeded the MicroVAX family, and shipped with the OpenVMS operating system. It was the last family of low-end VAX systems, as the platform was discontinued by Compaq.

The VAX 6000 is a discontinued family of minicomputers developed and manufactured by Digital Equipment Corporation (DEC) using processors implementing the VAX instruction set architecture (ISA). Originally, the VAX 6000 was intended to be a mid-range VAX product line complementing the VAX 8000, but with the introduction of the VAX 6000 Model 400 series, the older VAX 8000 was discontinued in favor of the VAX 6000, which offered slightly higher performance for half the cost. The VAX 6000 family supports Digital's VMS and ULTRIX operating systems.

The VAX 7000 and VAX 10000 are a discontinued family of high-end multiprocessor minicomputers developed and manufactured by Digital Equipment Corporation (DEC), introduced in July 1992. These systems use NVAX microprocessors implementing the VAX instruction set architecture, and run the OpenVMS operating system.

The VAX 8000 is a discontinued family of superminicomputers developed and manufactured by Digital Equipment Corporation (DEC) using processors implementing the VAX instruction set architecture (ISA).

The VAXft was a family of fault-tolerant minicomputers developed and manufactured by Digital Equipment Corporation (DEC) using processors implementing the VAX instruction set architecture (ISA). "VAXft" stood for "Virtual Address Extension, fault tolerant". These systems ran the OpenVMS operating system, and were first supported by VMS 5.4. Two layered software products, VAXft System Services and VMS Volume Shadowing, were required to support the fault-tolerant features of the VAXft and for the redundancy of data stored on hard disk drives.

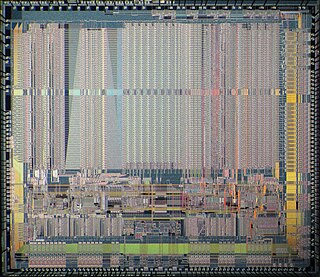

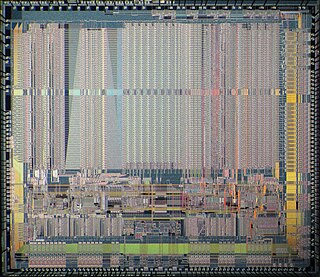

The Alpha 21064 is a microprocessor developed and fabricated by Digital Equipment Corporation that implemented the Alpha instruction set architecture (ISA). It was introduced as the DECchip 21064 before it was renamed in 1994. The 21064 is also known by its code name, EV4. It was announced in February 1992 with volume availability in September 1992. The 21064 was the first commercial implementation of the Alpha ISA, and the first microprocessor from Digital to be available commercially. It was succeeded by a derivative, the Alpha 21064A in October 1993. This last version was replaced by the Alpha 21164 in 1995.

The Alpha 21164, also known by its code name, EV5, is a microprocessor developed and fabricated by Digital Equipment Corporation that implemented the Alpha instruction set architecture (ISA). It was introduced in January 1995, succeeding the Alpha 21064A as Digital's flagship microprocessor. It was succeeded by the Alpha 21264 in 1998.

The Alpha 21264 is a Digital Equipment Corporation RISC microprocessor launched on 19 October 1998. The 21264 implemented the Alpha instruction set architecture (ISA).

Rigel was a microprocessor chip set developed and fabricated by Digital Equipment Corporation (DEC) that implemented the VAX instruction set architecture (ISA). It was introduced on 11 July 1989 with the introduction of the VAX 6000 Model 400, the first system to feature the chip set. Rigel was also used in the VAX 4000 Model 300 and VAXstation 3100 Model 76. Production Rigel CPUs were rated at 35 to 43 MHz.