Related Research Articles

PowerPC is a reduced instruction set computer (RISC) instruction set architecture (ISA) created by the 1991 Apple–IBM–Motorola alliance, known as AIM. PowerPC, as an evolving instruction set, has been named Power ISA since 2006, while the old name lives on as a trademark for some implementations of Power Architecture–based processors.

The AIM alliance, also known as the PowerPC alliance, was formed on October 2, 1991, between Apple, IBM, and Motorola. Its goal was to create an industry-wide open-standard computing platform based on the POWER instruction set architecture. It was intended to solve legacy problems, future-proof the industry, and compete with Microsoft's monopoly and the Wintel duopoly. The alliance yielded the launch of Taligent, Kaleida Labs, the PowerPC CPU family, the Common Hardware Reference Platform (CHRP) hardware platform standard, and Apple's Power Macintosh computer line.

Wintel is the partnership of Microsoft Windows and Intel producing personal computers using Intel x86-compatible processors running Microsoft Windows.

In computer architecture, 64-bit integers, memory addresses, or other data units are those that are 64 bits wide. Also, 64-bit central processing units (CPU) and arithmetic logic units (ALU) are those that are based on processor registers, address buses, or data buses of that size. A computer that uses such a processor is a 64-bit computer.

Cyrix Corporation was a microprocessor developer that was founded in 1988 in Richardson, Texas, as a specialist supplier of floating point units for 286 and 386 microprocessors. The company was founded by Tom Brightman and Jerry Rogers.

Common Hardware Reference Platform (CHRP) is a standard system architecture for PowerPC-based computer systems published jointly by IBM and Apple in 1995. Like its predecessor PReP, it was conceptualized as a design to allow various operating systems to run on an industry standard hardware platform, and specified the use of Open Firmware and RTAS for machine abstraction purposes. Unlike PReP, CHRP incorporated elements of the Power Macintosh architecture and was intended to support the classic Mac OS and NetWare, in addition to the four operating systems that had been ported to PReP at the time.

Geode was a series of x86-compatible system-on-a-chip (SoC) microprocessors and I/O companions produced by AMD, targeted at the embedded computing market.

A hypervisor, also known as a virtual machine monitor (VMM) or virtualizer, is a type of computer software, firmware or hardware that creates and runs virtual machines. A computer on which a hypervisor runs one or more virtual machines is called a host machine, and each virtual machine is called a guest machine. The hypervisor presents the guest operating systems with a virtual operating platform and manages the execution of the guest operating systems. Unlike an emulator, the guest executes most instructions on the native hardware. Multiple instances of a variety of operating systems may share the virtualized hardware resources: for example, Linux, Windows, and macOS instances can all run on a single physical x86 machine. This contrasts with operating-system–level virtualization, where all instances must share a single kernel, though the guest operating systems can differ in user space, such as different Linux distributions with the same kernel.

In computing, a programmable interrupt controller (PIC) is an integrated circuit that helps a microprocessor handle interrupt requests (IRQs) coming from multiple different sources which may occur simultaneously. It helps prioritize IRQs so that the CPU switches execution to the most appropriate interrupt handler (ISR) after the PIC assesses the IRQs' relative priorities. Common modes of interrupt priority include hard priorities, rotating priorities, and cascading priorities. PICs often allow mapping input to outputs in a configurable way. On the PC architecture PIC are typically embedded into a southbridge chip whose internal architecture is defined by the chipset vendor's standards.

Rosetta is a dynamic binary translator developed by Apple Inc. for macOS, an application compatibility layer between different instruction set architectures. It enables a transition to newer hardware, by automatically translating software. The name is a reference to the Rosetta Stone, the artifact which enabled translation of Egyptian hieroglyphs.

The Mac transition to Intel processors was the process of switching the central processing units (CPUs) of Apple's line of Mac and Xserve computers from PowerPC processors over to Intel's x86-64 processors. The change was announced at the 2005 Worldwide Developers Conference (WWDC) by then-Apple CEO Steve Jobs, who said Apple would gradually stop using PowerPC microprocessors supplied by Freescale and IBM.

In computing, Intel's Advanced Programmable Interrupt Controller (APIC) is a family of programmable interrupt controllers. As its name suggests, the APIC is more advanced than Intel's 8259 Programmable Interrupt Controller (PIC), particularly enabling the construction of multiprocessor systems. It is one of several architectural designs intended to solve interrupt routing efficiency issues in multiprocessor computer systems.

An end of interrupt (EOI) is a computing signal sent to a programmable interrupt controller (PIC) to indicate the completion of interrupt processing for a given interrupt. Interrupts are used to facilitate hardware signals sent to the processor that temporarily stop a running program and allow a special program, an interrupt handler, to run instead. An EOI is used to cause a PIC to clear the corresponding bit in the in-service register (ISR), and thus allow more interrupt requests (IRQs) of equal or lower priority to be generated by the PIC.

The Apple Network Server (ANS) was a line of PowerPC-based server computers designed, manufactured and sold by Apple Computer, Inc. from February 1996 to April 1997. It was codenamed "Shiner" and originally consisted of two models, the Network Server 500/132 and the Network Server 700/150, which got a companion model, the Network Server 700/200 with a faster CPU in November 1996.

In the x86 architecture, the CPUID instruction is a processor supplementary instruction allowing software to discover details of the processor. It was introduced by Intel in 1993 with the launch of the Pentium and SL-enhanced 486 processors.

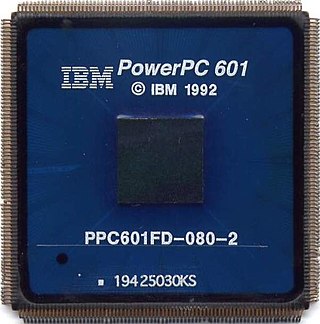

The PowerPC 600 family was the first family of PowerPC processors built. They were designed at the Somerset facility in Austin, Texas, jointly funded and staffed by engineers from IBM and Motorola as a part of the AIM alliance. Somerset was opened in 1992 and its goal was to make the first PowerPC processor and then keep designing general purpose PowerPC processors for personal computers. The first incarnation became the PowerPC 601 in 1993, and the second generation soon followed with the PowerPC 603, PowerPC 604 and the 64-bit PowerPC 620.

In computing, a device control register is a hardware register that controls some computer hardware device, for example a peripheral or an expansion card.

IBM Power microprocessors are designed and sold by IBM for servers and supercomputers. The name "POWER" was originally presented as an acronym for "Performance Optimization With Enhanced RISC". The Power line of microprocessors has been used in IBM's RS/6000, AS/400, pSeries, iSeries, System p, System i, and Power Systems lines of servers and supercomputers. They have also been used in data storage devices and workstations by IBM and by other server manufacturers like Bull and Hitachi.

References

- ↑ "OpenPIC Definition from PC Magazine Encyclopedia". Pcmag.com. 1994-12-01. Retrieved 2011-11-03.

- ↑ Brooke Crothers (20 March 1995). AMD, Cyrix offer up alternative SMP spec. InfoWorld. p. 8. ISSN 0199-6649.

- ↑ André D. Balsa, Note attached to "Linux Benchmarking: Part III -- Interpreting Benchmark Results" appearing in Issue 24 of Linux Gazette, January 1998

- 1 2 IBM Multiprocessor Interrupt Controller. Data Book Archived 2014-02-23 at the Wayback Machine

- ↑ Arca Systems TTAP Evaluation Facility, "The IBM Corporation RS/6000 Distributed System Running AIX Version 4.3.1. TCSEC Evaluated C2 Security", p. 29

- ↑ RS/6000 7046 Model B50 Handbook, November 1999, IBM document G24-7046-00, p. 107

- ↑ Yellowknife Reference Platform Hardware Design Manual, p. 11

- ↑ Macintosh Technology in the Common Hardware Reference Platform, section "2.4.7 Open PIC Interrupt Controller", p. 11, ISBN 155860393X

- ↑ Take a Look Inside the G5-Based Dual-Processor Power Mac

- ↑ Power Mac G5 Developer Note (Legacy), p. 26

- ↑ Freescale MPIC Interrupt Controller Node

- ↑ "linux/Documentation/virtual/kvm/devices/mpic.txt at master". Github.com. 2013-04-30. Retrieved 2014-02-12.