Chemical vapor deposition (CVD) is a vacuum deposition method used to produce high-quality, and high-performance, solid materials. The process is often used in the semiconductor industry to produce thin films.

MEMS is the technology of microscopic devices incorporating both electronic and moving parts. MEMS are made up of components between 1 and 100 micrometres in size, and MEMS devices generally range in size from 20 micrometres to a millimetre, although components arranged in arrays can be more than 1000 mm2. They usually consist of a central unit that processes data and several components that interact with the surroundings.

Solder is a fusible metal alloy used to create a permanent bond between metal workpieces. Solder is melted in order to wet the parts of the joint, where it adheres to and connects the pieces after cooling. Metals or alloys suitable for use as solder should have a lower melting point than the pieces to be joined. The solder should also be resistant to oxidative and corrosive effects that would degrade the joint over time. Solder used in making electrical connections also needs to have favorable electrical characteristics.

Brazing is a metal-joining process in which two or more metal items are joined by melting and flowing a filler metal into the joint, with the filler metal having a lower melting point than the adjoining metal.

In chemistry, a dangling bond is an unsatisfied valence on an immobilized atom. An atom with a dangling bond is also referred to as an immobilized free radical or an immobilized radical, a reference to its structural and chemical similarity to a free radical.

A superalloy, or high-performance alloy, is an alloy with the ability to operate at a high fraction of its melting point. Key characteristics of a superalloy include mechanical strength, thermal creep deformation resistance, surface stability, and corrosion and oxidation resistance.

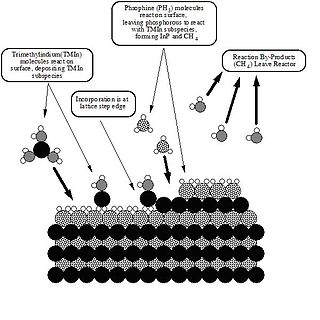

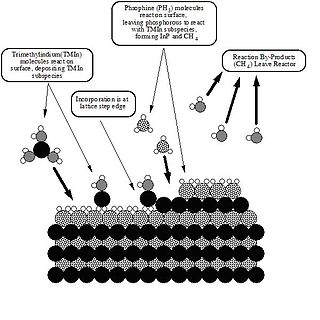

Metalorganic vapour-phase epitaxy (MOVPE), also known as organometallic vapour-phase epitaxy (OMVPE) or metalorganic chemical vapour deposition (MOCVD), is a chemical vapour deposition method used to produce single- or polycrystalline thin films. It is a process for growing crystalline layers to create complex semiconductor multilayer structures. In contrast to molecular-beam epitaxy (MBE), the growth of crystals is by chemical reaction and not physical deposition. This takes place not in vacuum, but from the gas phase at moderate pressures. As such, this technique is preferred for the formation of devices incorporating thermodynamically metastable alloys, and it has become a major process in the manufacture of optoelectronics, such as Light-emitting diodes, its most widespread application. It was first demonstrated in 1967 at North American Aviation Autonetics Division in Anaheim CA by Harold M. Manasevit.

In microfabrication, thermal oxidation is a way to produce a thin layer of oxide on the surface of a wafer. The technique forces an oxidizing agent to diffuse into the wafer at high temperature and react with it. The rate of oxide growth is often predicted by the Deal–Grove model. Thermal oxidation may be applied to different materials, but most commonly involves the oxidation of silicon substrates to produce silicon dioxide.

A metal gate, in the context of a lateral metal–oxide–semiconductor (MOS) stack, is the gate electrode separated by an oxide from the transistor's channel – the gate material is made from a metal. In most MOS transistors since about the mid-1970s, the "M" for metal has been replaced by polysilicon, but the name remained.

Adhesive bonding describes a wafer bonding technique with applying an intermediate layer to connect substrates of different types of materials. Those connections produced can be soluble or insoluble. The commercially available adhesive can be organic or inorganic and is deposited on one or both substrate surfaces. Adhesives, especially the well-established SU-8, and benzocyclobutene (BCB), are specialized for MEMS or electronic component production.

The vapor–liquid–solid method (VLS) is a mechanism for the growth of one-dimensional structures, such as nanowires, from chemical vapor deposition. The growth of a crystal through direct adsorption of a gas phase on to a solid surface is generally very slow. The VLS mechanism circumvents this by introducing a catalytic liquid alloy phase which can rapidly adsorb a vapor to supersaturation levels, and from which crystal growth can subsequently occur from nucleated seeds at the liquid–solid interface. The physical characteristics of nanowires grown in this manner depend, in a controllable way, upon the size and physical properties of the liquid alloy.

A copper indium gallium selenide solar cell is a thin-film solar cell used to convert sunlight into electric power. It is manufactured by depositing a thin layer of copper indium gallium selenide solid solution on glass or plastic backing, along with electrodes on the front and back to collect current. Because the material has a high absorption coefficient and strongly absorbs sunlight, a much thinner film is required than of other semiconductor materials.

Thermocompression bonding describes a wafer bonding technique and is also referred to as diffusion bonding, pressure joining, thermocompression welding or solid-state welding. Two metals, e.g. gold-gold (Au), are brought into atomic contact applying force and heat simultaneously. The diffusion requires atomic contact between the surfaces due to the atomic motion. The atoms migrate from one crystal lattice to the other one based on crystal lattice vibration. This atomic interaction sticks the interface together. The diffusion process is described by the following three processes:

Crystalline silicon or (c-Si) Is the crystalline forms of silicon, either polycrystalline silicon, or monocrystalline silicon. Crystalline silicon is the dominant semiconducting material used in photovoltaic technology for the production of solar cells. These cells are assembled into solar panels as part of a photovoltaic system to generate solar power from sunlight.

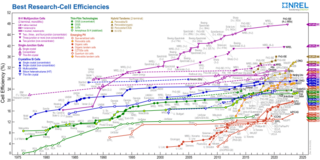

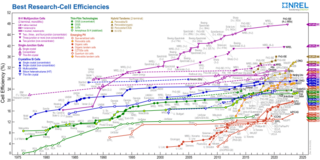

There are currently many research groups active in the field of photovoltaics in universities and research institutions around the world. This research can be categorized into three areas: making current technology solar cells cheaper and/or more efficient to effectively compete with other energy sources; developing new technologies based on new solar cell architectural designs; and developing new materials to serve as more efficient energy converters from light energy into electric current or light absorbers and charge carriers.

Direct bonding, or fusion bonding, describes a wafer bonding process without any additional intermediate layers. The bonding process is based on chemical bonds between two surfaces of any material possible meeting numerous requirements. These requirements are specified for the wafer surface as sufficiently clean, flat and smooth. Otherwise unbonded areas so called voids, i.e. interface bubbles, can occur.

Anodic bonding is a wafer bonding process to seal glass to either silicon or metal without introducing an intermediate layer; it is commonly used to seal glass to silicon wafers in electronics and microfluidics. This bonding technique, also known as field assisted bonding or electrostatic sealing, is mostly used for connecting silicon/glass and metal/glass through electric fields. The requirements for anodic bonding are clean and even wafer surfaces and atomic contact between the bonding substrates through a sufficiently powerful electrostatic field. Also necessary is the use of borosilicate glass containing a high concentration of alkali ions. The coefficient of thermal expansion (CTE) of the processed glass needs to be similar to those of the bonding partner.

Glass frit bonding, also referred to as glass soldering or seal glass bonding, describes a wafer bonding technique with an intermediate glass layer. It is a widely used encapsulation technology for surface micro-machined structures, e.g., accelerometers or gyroscopes. This technique utilizes low melting-point glass and therefore provides various advantages including that viscosity of glass decreases with an increase of temperature. The viscous flow of glass has effects to compensate and planarize surface irregularities, convenient for bonding wafers with a high roughness due to plasma etching or deposition. A low viscosity promotes hermetically sealed encapsulation of structures based on a better adaption of the structured shapes. Further, the coefficient of thermal expansion (CTE) of the glass material is adapted to silicon. This results in low stress in the bonded wafer pair. The glass has to flow and wet the soldered surfaces well below the temperature where deformation or degradation of either of the joined materials or nearby structures occurs. The usual temperature of achieving flowing and wetting is between 450 and 550 °C.

Reactive bonding describes a wafer bonding procedure using highly reactive nanoscale multilayer systems as an intermediate layer between the bonding substrates. The multilayer system consists of two alternating different thin metallic films. The self-propagating exothermic reaction within the multilayer system contributes the local heat to bond the solder films. Based on the limited temperature the substrate material is exposed, temperature-sensitive components and materials with different CTEs, i.e. metals, polymers and ceramics, can be used without thermal damage.

Transient liquid phase diffusion bonding (TLPDB) is a joining process that has been applied for bonding many metallic and ceramic systems which cannot be bonded by conventional fusion welding techniques. The bonding process produces joints with a uniform composition profile, tolerant of surface oxides and geometrical defects. The bonding technique has been exploited in a wide range of applications, from the production and repair of turbine engines in the aerospace industry, to nuclear power plants, and in making connections to integrated circuit dies as a part of the microelectronics industry.