A printed circuit board (PCB), also called printed wiring board (PWB), is a medium used to connect or "wire" components to one another in a circuit. It takes the form of a laminated sandwich structure of conductive and insulating layers: each of the conductive layers is designed with a pattern of traces, planes and other features etched from one or more sheet layers of copper laminated onto and/or between sheet layers of a non-conductive substrate. Electrical components may be fixed to conductive pads on the outer layers in the shape designed to accept the component's terminals, generally by means of soldering, to both electrically connect and mechanically fasten them to it. Another manufacturing process adds vias, plated-through holes that allow interconnections between layers.

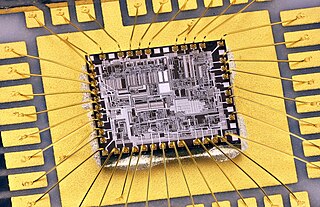

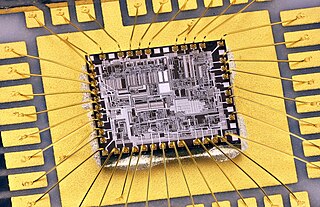

Wire bonding is the method of making interconnections between an integrated circuit (IC) or other semiconductor device and its packaging during semiconductor device fabrication. Although less common, wire bonding can be used to connect an IC to other electronics or to connect from one printed circuit board (PCB) to another. Wire bonding is generally considered the most cost-effective and flexible interconnect technology and is used to assemble the vast majority of semiconductor packages. Wire bonding can be used at frequencies above 100 GHz.

In semiconductor technology, copper interconnects are interconnects made of copper. They are used in silicon integrated circuits (ICs) to reduce propagation delays and power consumption. Since copper is a better conductor than aluminium, ICs using copper for their interconnects can have interconnects with narrower dimensions, and use less energy to pass electricity through them. Together, these effects lead to ICs with better performance. They were first introduced by IBM, with assistance from Motorola, in 1997.

Flexible electronics, also known as flex circuits, is a technology for assembling electronic circuits by mounting electronic devices on flexible plastic substrates, such as polyimide, PEEK or transparent conductive polyester film. Additionally, flex circuits can be screen printed silver circuits on polyester. Flexible electronic assemblies may be manufactured using identical components used for rigid printed circuit boards, allowing the board to conform to a desired shape, or to flex during its use.

A via is an electrical connection between two or more metal layers, and are commonly used in printed circuit boards (PCB). Essentially a via is a small drilled hole that goes through two or more adjacent layers; the hole is plated with metal that forms an electrical connection through the insulating layers.

The back end of line (BEOL) is the second portion of IC fabrication where the individual devices get interconnected with wiring on the wafer, the metalization layer. Common metals are copper and aluminum. BEOL generally begins when the first layer of metal is deposited on the wafer. BEOL includes contacts, insulating layers (dielectrics), metal levels, and bonding sites for chip-to-package connections.

Conformal coating is a protective, breathable coating of thin polymeric film applied to printed circuit boards (PCBs). Conformal coatings are typically applied at 25–250 μm to the electronic circuitry and provide protection against moisture and other harsher conditions.

Flat no-leads packages such as quad-flat no-leads (QFN) and dual-flat no-leads (DFN) physically and electrically connect integrated circuits to printed circuit boards. Flat no-leads, also known as micro leadframe (MLF) and SON, is a surface-mount technology, one of several package technologies that connect ICs to the surfaces of PCBs without through-holes. Flat no-lead is a near chip scale plastic encapsulated package made with a planar copper lead frame substrate. Perimeter lands on the package bottom provide electrical connections to the PCB. Flat no-lead packages usually, but not always, include an exposed thermally conductive pad to improve heat transfer out of the IC. Heat transfer can be further facilitated by metal vias in the thermal pad. The QFN package is similar to the quad-flat package (QFP), and a ball grid array (BGA).

IPC is a trade association whose aim is to standardize the assembly and production requirements of electronic equipment and assemblies. IPC is headquartered in Bannockburn, Illinois, United States with additional offices in Washington, D.C. Atlanta, Ga., and Miami, Fla. in the United States, and overseas offices in China, Japan, Thailand, India, Germany, and Belgium.

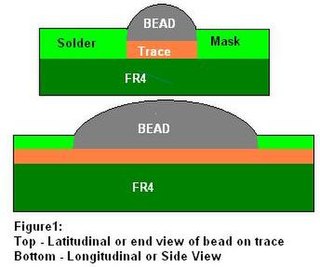

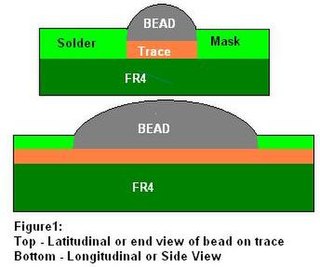

Bead probe technology (BPT) is technique used to provide electrical access to printed circuit board (PCB) circuitry for performing in-circuit testing (ICT). It makes use of small beads of solder placed onto the board's traces to allow measuring and controlling of the signals using a test probe. This permits test access to boards on which standard ICT test pads are not feasible due to space constraints.

The thermal copper pillar bump, also known as the "thermal bump", is a thermoelectric device made from thin-film thermoelectric material embedded in flip chip interconnects for use in electronics and optoelectronic packaging, including: flip chip packaging of CPU and GPU integrated circuits (chips), laser diodes, and semiconductor optical amplifiers (SOA). Unlike conventional solder bumps that provide an electrical path and a mechanical connection to the package, thermal bumps act as solid-state heat pumps and add thermal management functionality locally on the surface of a chip or to another electrical component. The diameter of a thermal bump is 238 μm and 60 μm high.

Electronic components have a wide range of failure modes. These can be classified in various ways, such as by time or cause. Failures can be caused by excess temperature, excess current or voltage, ionizing radiation, mechanical shock, stress or impact, and many other causes. In semiconductor devices, problems in the device package may cause failures due to contamination, mechanical stress of the device, or open or short circuits.

Pad cratering is a mechanically induced fracture in the resin between copper foil and outermost layer of fiberglass of a printed circuit board (PCB). It may be within the resin or at the resin to fiberglass interface.

Physics of failure is a technique under the practice of reliability design that leverages the knowledge and understanding of the processes and mechanisms that induce failure to predict reliability and improve product performance.

Solder fatigue is the mechanical degradation of solder due to deformation under cyclic loading. This can often occur at stress levels below the yield stress of solder as a result of repeated temperature fluctuations, mechanical vibrations, or mechanical loads. Techniques to evaluate solder fatigue behavior include finite element analysis and semi-analytical closed-form equations.

Digital image correlation analyses have applications in material property characterization, displacement measurement, and strain mapping. As such, DIC is becoming an increasingly popular tool when evaluating the thermo-mechanical behavior of electronic components and systems.

In electronics, a cross section, cross-section, or microsection, is a prepared electronics sample that allows analysis at a plane that cuts through the sample. It is a destructive technique requiring that a portion of the sample be cut or ground away to expose the internal plane for analysis. They are commonly prepared for research, manufacturing quality assurance, supplier conformity, and failure analysis. Printed wiring boards (PWBs) and electronic components and their solder joints are common cross sectioned samples. The features of interest to be analyzed in cross section can be nanometer-scale metal and dielectric layers in semiconductors up to macroscopic features such as the amount of solder that has filled into a large, 0.125in (3.18mm) diameter plated through hole.

Conductive anodic filament, also called CAF, is a metallic filament that forms from an electrochemical migration process and is known to cause printed circuit board (PCB) failures.

In integrated circuits (ICs), interconnects are structures that connect two or more circuit elements together electrically. The design and layout of interconnects on an IC is vital to its proper function, performance, power efficiency, reliability, and fabrication yield. The material interconnects are made from depends on many factors. Chemical and mechanical compatibility with the semiconductor substrate and the dielectric between the levels of interconnect is necessary, otherwise barrier layers are needed. Suitability for fabrication is also required; some chemistries and processes prevent the integration of materials and unit processes into a larger technology (recipe) for IC fabrication. In fabrication, interconnects are formed during the back-end-of-line after the fabrication of the transistors on the substrate.

Glossary of microelectronics manufacturing terms