AVR is a family of microcontrollers developed since 1996 by Atmel, acquired by Microchip Technology in 2016. These are modified Harvard architecture 8-bit RISC single-chip microcontrollers. AVR was one of the first microcontroller families to use on-chip flash memory for program storage, as opposed to one-time programmable ROM, EPROM, or EEPROM used by other microcontrollers at the time.

XScale is a microarchitecture for central processing units initially designed by Intel implementing the ARM architecture instruction set. XScale comprises several distinct families: IXP, IXC, IOP, PXA and CE, with some later models designed as system-on-a-chip (SoC). Intel sold the PXA family to Marvell Technology Group in June 2006. Marvell then extended the brand to include processors with other microarchitectures, like Arm's Cortex.

The PowerPC 970, PowerPC 970FX, and PowerPC 970MP are 64-bit PowerPC processors from IBM introduced in 2002. When used in PowerPC-based Macintosh computers, Apple referred to them as the PowerPC G5.

The PowerPC 400 family is a line of 32-bit embedded RISC processor cores based on the PowerPC or Power ISA instruction set architectures. The cores are designed to fit inside specialized applications ranging from system-on-a-chip (SoC) microcontrollers, network appliances, application-specific integrated circuits (ASICs) and field-programmable gate arrays (FPGAs) to set-top boxes, storage devices and supercomputers.

The R3000 is a 32-bit RISC microprocessor chipset developed by MIPS Computer Systems that implemented the MIPS I instruction set architecture (ISA). Introduced in June 1988, it was the second MIPS implementation, succeeding the R2000 as the flagship MIPS microprocessor. It operated at 20, 25 and 33.33 MHz.

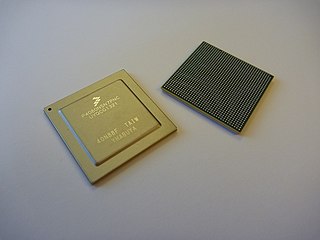

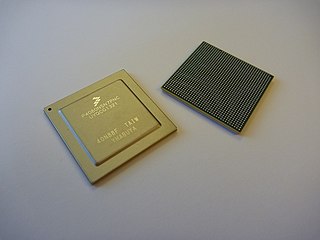

PowerQUICC is the name for several PowerPC- and Power ISA-based microcontrollers from Freescale Semiconductor. They are built around one or more PowerPC cores and the Communications Processor Module which is a separate RISC core specialized in such tasks such as I/O, communications, ATM, security acceleration, networking and USB. Many components are System-on-a-chip designs tailor-made for embedded applications.

PWRficient is a microprocessor series by P.A. Semi where the PA6T-1682M was the only one that became an actual product.

The PowerPC e600 is a family of 32-bit PowerPC microprocessor cores developed by Freescale for primary use in high performance system-on-a-chip (SoC) designs with speed ranging over 2 GHz, thus making them ideal for high performance routing and telecommunications applications. The e600 is the continuation of the PowerPC 74xx design.

QorIQ is a brand of ARM-based and Power ISA–based communications microprocessors from NXP Semiconductors. It is the evolutionary step from the PowerQUICC platform, and initial products were built around one or more e500mc cores and came in five different product platforms, P1, P2, P3, P4, and P5, segmented by performance and functionality. The platform keeps software compatibility with older PowerPC products such as the PowerQUICC platform. In 2012 Freescale announced ARM-based QorIQ offerings beginning in 2013.

EFM32 Gecko MCUs are a family of mixed-signal 32-bit microcontroller integrated circuits from Energy Micro based on ARM Cortex-M CPUs, including the Cortex-M0+, Cortex-M3 and Cortex-M4.

The R4200 is a microprocessor designed by MIPS Technologies, Inc. (MTI) that implemented the MIPS III instruction set architecture (ISA). It was also known as the VRX during development. The microprocessor was licensed to NEC, and the company fabricated and marketed it as the VR4200. The first VR4200, an 80 MHz part, was introduced in 1993. A faster 100 MHz part became available in 1994.

Zero ASIC Corporation, formerly Adapteva, Inc., is a fabless semiconductor company focusing on low power many core microprocessor design. The company was the second company to announce a design with 1,000 specialized processing cores on a single integrated circuit.

IBM Power microprocessors are designed and sold by IBM for servers and supercomputers. The name "POWER" was originally presented as an acronym for "Performance Optimization With Enhanced RISC". The Power line of microprocessors has been used in IBM's RS/6000, AS/400, pSeries, iSeries, System p, System i, and Power Systems lines of servers and supercomputers. They have also been used in data storage devices and workstations by IBM and by other server manufacturers like Bull and Hitachi.

RISC-V is an open standard instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles. Unlike most other ISA designs, RISC-V is provided under royalty-free open-source licenses. A number of companies are offering or have announced RISC-V hardware; open source operating systems with RISC-V support are available, and the instruction set is supported in several popular software toolchains.

The MSP432 is a mixed-signal microcontroller family from Texas Instruments. It is based on a 32-bit ARM Cortex-M4F CPU, and extends their 16-bit MSP430 line, with a larger address space for code and data, and faster integer and floating point calculation than the MSP430. Like the MSP430, it has a number of built-in peripheral devices, and is designed for low power requirements. In 2021, TI confirmed that the MSP432 has been discontinued and "there will be no new MSP432 products".

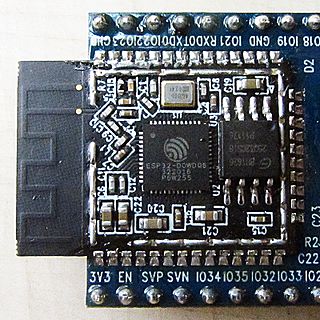

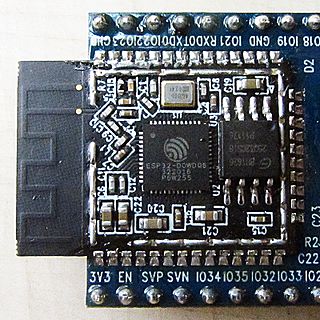

ESP32 is a series of low-cost, low-power system on a chip microcontrollers with integrated Wi-Fi and dual-mode Bluetooth. The ESP32 series employs either a Tensilica Xtensa LX6 microprocessor in both dual-core and single-core variations, Xtensa LX7 dual-core microprocessor or a single-core RISC-V microprocessor and includes built-in antenna switches, RF balun, power amplifier, low-noise receive amplifier, filters, and power-management modules. ESP32 is created and developed by Espressif Systems, a Chinese company based in Shanghai, and is manufactured by TSMC using their 40 nm process. It is a successor to the ESP8266 microcontroller.

VEGA Microprocessors are a portfolio of indigenous processors developed by C-DAC. The portfolio includes several 32-bit/64-bit Single/Multi-core Superscalar In-order/Out-of-Order high performance processors based on the RISC-V ISA. Also features India's first indigenous 64-bit, superscalar, Out-of-order processor which is the main highlight of this portfolio. The Centre for Development of Advanced Computing (C-DAC) is an autonomous Scientific Society, operating under the Ministry of Electronics and Information Technology (MeitY), Govt. of India. The Microprocessor Development Programme (MDP) was initiated and funded by MeitY with the mission objective to design and develop indigenously, a family of Microprocessors, related IPs and the complete ecosystem to enable fully indigenous product development that meets various requirements in the strategic, industrial and commercial sectors. As part of the project C-DAC has successfully developed the VEGA series of microprocessors in soft IP form, which include32-bit Single-core (In-order), 64-bit Single-core, 64-bit Dual-core (Out-of-order), and 64-bit Quad-core (Out-of-order). These high-performance processors are based on the open-source RISC-V Instruction Set Architecture. The tape out of some of these processor chips have also been planned.