Related Research Articles

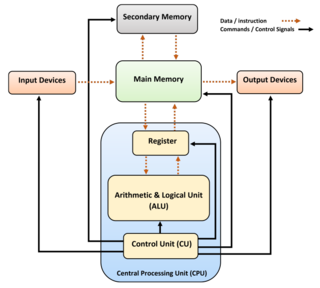

A microprocessor is a computer processor for which the data processing logic and control is included on a single integrated circuit (IC), or a small number of ICs. The microprocessor contains the arithmetic, logic, and control circuitry required to perform the functions of a computer's central processing unit (CPU). The IC is capable of interpreting and executing program instructions and performing arithmetic operations. The microprocessor is a multipurpose, clock-driven, register-based, digital integrated circuit that accepts binary data as input, processes it according to instructions stored in its memory, and provides results as output. Microprocessors contain both combinational logic and sequential digital logic, and operate on numbers and symbols represented in the binary number system.

David Andrew Patterson is an American computer pioneer and academic who has held the position of professor of computer science at the University of California, Berkeley since 1976. He announced retirement in 2016 after serving nearly forty years, becoming a distinguished software engineer at Google. He currently is vice chair of the board of directors of the RISC-V Foundation, and the Pardee Professor of Computer Science, Emeritus at UC Berkeley.

The POWER5 is a microprocessor developed and fabricated by IBM. It is an improved version of the POWER4. The principal improvements are support for simultaneous multithreading (SMT) and an on-die memory controller. The POWER5 is a dual-core microprocessor, with each core supporting one physical thread and two logical threads, for a total of two physical threads and four logical threads.

In computer engineering, out-of-order execution is a paradigm used in high-performance central processing units to make use of instruction cycles that would otherwise be wasted. In this paradigm, a processor executes instructions in an order governed by the availability of input data and execution units, rather than by their original order in a program. In doing so, the processor can avoid being idle while waiting for the preceding instruction to complete and can, in the meantime, process the next instructions that are able to run immediately and independently.

David A. Bader is a Distinguished Professor and Director of the Institute for Data Science at the New Jersey Institute of Technology. Previously, he served as the Chair of the Georgia Institute of Technology School of Computational Science & Engineering, where he was also a founding professor, and the executive director of High-Performance Computing at the Georgia Tech College of Computing. In 2007, he was named the first director of the Sony Toshiba IBM Center of Competence for the Cell Processor at Georgia Tech.

The POWER4 is a microprocessor developed by International Business Machines (IBM) that implemented the 64-bit PowerPC and PowerPC AS instruction set architectures. Released in 2001, the POWER4 succeeded the POWER3 and RS64 microprocessors, enabling RS/6000 and eServer iSeries models of AS/400 computer servers to run on the same processor, as a step toward converging the two lines. The POWER4 was a multicore microprocessor, with two cores on a single die, the first non-embedded microprocessor to do so. POWER4 Chip was first commercially available multiprocessor chip. The original POWER4 had a clock speed of 1.1 and 1.3 GHz, while an enhanced version, the POWER4+, reached a clock speed of 1.9 GHz. The PowerPC 970 is a derivative of the POWER4.

Harry L. "Nick" Tredennick was an American manager, inventor, VLSI design engineer and author who was involved in the development for Motorola's MC68000 and for IBM's Micro/370 microprocessors. He held BSEE and MSEE degrees from Texas Tech University, and a Ph.D. in Electrical Engineering from the University of Texas at Austin. Tredennick was named a Fellow of the IEEE; the citation reads "For the design and implementation of the execution unit and controller of the MC68000 workstation microprocessor".

The PowerPC 600 family was the first family of PowerPC processors built. They were designed at the Somerset facility in Austin, Texas, jointly funded and staffed by engineers from IBM and Motorola as a part of the AIM alliance. Somerset was opened in 1992 and its goal was to make the first PowerPC processor and then keep designing general purpose PowerPC processors for personal computers. The first incarnation became the PowerPC 601 in 1993, and the second generation soon followed with the PowerPC 603, PowerPC 604 and the 64-bit PowerPC 620.

The International Symposium on Computer Architecture (ISCA) is an annual academic conference on computer architecture, generally viewed as the top-tier in the field. Association for Computing Machinery's Special Interest Group on Computer Architecture and Institute of Electrical and Electronics Engineers Computer Society are technical sponsors.

Thomas Martin Conte is the Associate Dean for Research and Professor of Computer Science at Georgia Institute of Technology College of Computing; and, since 2011, also Professor of Electrical and Computer Engineering at Georgia Institute of Technology College of Engineering. He is a fellow of Institute of Electrical and Electronics Engineers (IEEE). He served as the president of the IEEE Computer Society in 2015.

Krishna V. Palem is a computer scientist and engineer of Indian origin and is the Kenneth and Audrey Kennedy Professor of Computing at Rice University and the director of Institute for Sustainable Nanoelectronics (ISNE) at Nanyang Technological University (NTU). He is recognized for his "pioneering contributions to the algorithmic, compilation, and architectural foundations of embedded computing", as stated in the citation of his 2009 Wallace McDowell Award, the "highest technical award made solely by the IEEE Computer Society".

Mark D. Papermaster is an American business executive who is the chief technology officer (CTO) and executive vice president for technology and engineering at Advanced Micro Devices (AMD). On January 25, 2019 he was promoted to AMD's Executive Vice President.

In computer science and computer engineering, computer architecture is a description of the structure of a computer system made from component parts. It can sometimes be a high-level description that ignores details of the implementation. At a more detailed level, the description may include the instruction set architecture design, microarchitecture design, logic design, and implementation.

The IEEE/ACM International Symposium on Microarchitecture® (MICRO) is an annual academic conference on microarchitecture, generally viewed as the top-tier academic conference on computer architecture. It is not to be confused with a micro-conference. Particularly within the domains of microarchitecture and Code generation (compiler), MICRO is unrivaled and esteemed as the premier forum. Association for Computing Machinery's Special Interest Group on Microarchitecture and Institute of Electrical and Electronics Engineers Computer Society are technical sponsors.

Margaret Martonosi is an American computer scientist who is currently the Hugh Trumbull Adams '35 Professor of Computer Science at Princeton University. Martonosi is noted for her research in computer architecture and mobile computing with a particular focus on power-efficiency.

Bijan Davari is an Iranian-American electrical engineer. He is an IBM Fellow and Vice President at IBM Thomas J Watson Research Center, Yorktown Hts, NY. His pioneering work in the miniaturization of semiconductor devices changed the world of computing. His research led to the first generation of voltage-scaled deep-submicron CMOS with sufficient performance to totally replace bipolar technology in IBM mainframes and enable new high-performance UNIX servers. As head of IBM’s Semiconductor Research Center (SRDC), he led IBM into the use of Copper interconnect, silicon on insulator (SOI), and Embedded DRAM before its rivals. He is a member of the U.S. National Academy of Engineering and is known for his seminal contributions to the field of CMOS technology. He is an IEEE Fellow, recipient of the J J Ebers Award in 2005 and IEEE Andrew S. Grove Award in 2010. At the present time, he leads the Next Generation Systems Area of research.

Lizy Kurian John is an Indian American electrical engineer, who is currently the Cullen Trust for Higher Education Endowed Professor in the Department of Electrical and Computer Engineering at the University of Texas at Austin. She received her Ph.D. in computer engineering from The Pennsylvania State University in 1993. She joined The University of Texas Austin faculty in 1996. Her research is in the areas of computer architecture, multicore processors, memory systems, performance evaluation and benchmarking, workload characterization, and reconfigurable computing.

Nader Bagherzadeh is a professor of computer engineering in the Department of Electrical Engineering and Computer Science at the University of California, Irvine, where he served as a chair from 1998 to 2003. Bagherzadeh has been involved in research and development in the areas of: Computer Architecture, Reconfigurable Computing, VLSI Chip Design, Network-on-Chip, 3D chips, Sensor Networks, Computer Graphics, Memory and Embedded Systems. Bagherzadeh was named Fellow of the Institute of Electrical and Electronics Engineers (IEEE) in 2014 for contributions to the design and analysis of coarse-grained reconfigurable processor architectures. Bagherzadeh has published more than 400 articles in peer-reviewed journals and conferences. He was with AT&T Bell Labs from 1980 to 1984.

Timothy M. Pinkston is an American computer engineer, researcher, educator and administrator whose work is focused in the area of computer architecture. He holds the George Pfleger Chair in Electrical and Computer Engineering and is a Professor of Electrical and Computer Engineering at University of Southern California (USC). He also serves in an administrative role as Vice Dean for Faculty Affairs at the USC Viterbi School of Engineering.

Trevor Mudge is a computer scientist, academic and researcher. He is the Bredt Family Chair of Computer Science and Engineering, and Professor of Electrical Engineering and Computer Science at the University of Michigan.

References

- ↑ Quentin Hardy (2011-11-07). "AMD Betting on Power Consumption". New York Times. Retrieved 2014-06-24.

- ↑ Association for Computing Machinery (2013-12-07). "ACM 2007 Plenary Speakers". ACM. Retrieved 2014-06-24.

- ↑ Charles R. Moore (2009). "Microarchitecture in the system-level integration era". MICRO 41 Proceedings of the 41st Annual IEEE/ACM International Symposium on Microarchitecture: i.

- ↑ San Jose Mercury News (2012-05-02). "Charles Moore Obituary". San Jose Mercury News. Retrieved 2014-06-24.

- ↑ Doug Burger; Stephen W. Keckler; Mark Papermaster (2012). "Charles R. (Chuck) Moore (1961—2012)". IEEE Micro. 32 (4 (July 2012)): 3–5. doi:10.1109/MM.2012.61.