Related Research Articles

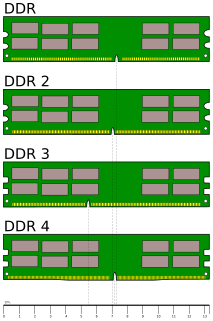

Double Data Rate Synchronous Dynamic Random-Access Memory is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) class of memory integrated circuits used in computers. DDR SDRAM, also retroactively called DDR1 SDRAM, has been superseded by DDR2 SDRAM, DDR3 SDRAM, DDR4 SDRAM and DDR5 SDRAM. None of its successors are forward or backward compatible with DDR1 SDRAM, meaning DDR2, DDR3, DDR4 and DDR5 memory modules will not work in DDR1-equipped motherboards, and vice versa.

Synchronous dynamic random-access memory is any DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal.

A DIMM or dual in-line memory module, commonly called a RAM stick, comprises a series of dynamic random-access memory integrated circuits. These modules are mounted on a printed circuit board and designed for use in personal computers, workstations, printers, and servers. DIMMs began to replace SIMMs as the predominant type of memory module as Intel P5-based Pentium processors began to gain market share.

Rambus DRAM (RDRAM), and its successors Concurrent Rambus DRAM (CRDRAM) and Direct Rambus DRAM (DRDRAM), are types of synchronous dynamic random-access memory (SDRAM) developed by Rambus from the 1990s through to the early-2000s. The third-generation of Rambus DRAM, DRDRAM was replaced by XDR DRAM. Rambus DRAM was developed for high-bandwidth applications, and was positioned by Rambus as replacement for various types of contemporary memories, such as SDRAM.

Double Data Rate 2 Synchronous Dynamic Random-Access Memory is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) interface. It superseded the original DDR SDRAM specification, and was itself superseded by DDR3 SDRAM. DDR2 DIMMs are neither forward compatible with DDR3 nor backward compatible with DDR.

A SO-DIMM or small outline DIMM, is a type of computer memory built using integrated circuits. A SO-DIMM is a smaller alternative to a DIMM, being roughly half the physical size of a regular DIMM.

In computing, a computer bus operating with double data rate (DDR) transfers data on both the rising and falling edges of the clock signal. This is also known as double pumped, dual-pumped, and double transition. The term toggle mode is used in the context of NAND flash memory.

In the fields of digital electronics and computer hardware, multi-channel memory architecture is a technology that increases the data transfer rate between the DRAM memory and the memory controller by adding more channels of communication between them. Theoretically, this multiplies the data rate by exactly the number of channels present. Dual-channel memory employs two channels. The technique goes back as far as the 1960s having been used in IBM System/360 Model 91 and in CDC 6600.

Registeredmemory modules have a register between the DRAM modules and the system's memory controller. They place less electrical load on the memory controller and allow single systems to remain stable with more memory modules than they would have otherwise. When compared with registered memory, conventional memory is usually referred to as unbuffered memory or unregistered memory. When manufactured as a dual in-line memory module (DIMM), a registered memory module is called an RDIMM, while unregistered memory is called UDIMM or simply DIMM.

In computing, serial presence detect (SPD) is a standardized way to automatically access information about a memory module. Earlier 72-pin SIMMs included five pins that provided five bits of parallel presence detect (PPD) data, but the 168-pin DIMM standard changed to a serial presence detect to encode much more information.

Double Data Rate 3 Synchronous Dynamic Random-Access Memory is a type of synchronous dynamic random-access memory (SDRAM) with a high bandwidth interface, and has been in use since 2007. It is the higher-speed successor to DDR and DDR2 and predecessor to DDR4 synchronous dynamic random-access memory (SDRAM) chips. DDR3 SDRAM is neither forward nor backward compatible with any earlier type of random-access memory (RAM) because of different signaling voltages, timings, and other factors.

Fully Buffered DIMM is a memory technology that can be used to increase reliability and density of memory systems. Unlike the parallel bus architecture of traditional DRAMs, an FB-DIMM has a serial interface between the memory controller and the advanced memory buffer (AMB). Conventionally, data lines from the memory controller have to be connected to data lines in every DRAM module, i.e. via multidrop buses. As the memory width increases together with the access speed, the signal degrades at the interface between the bus and the device. This limits the speed and memory density, so FB-DIMMs take a different approach to solve the problem.

The memory controller is a digital circuit that manages the flow of data going to and from the computer's main memory. A memory controller can be a separate chip or integrated into another chip, such as being placed on the same die or as an integral part of a microprocessor; in the latter case, it is usually called an integrated memory controller (IMC). A memory controller is sometimes also called a memory chip controller (MCC) or a memory controller unit (MCU).

HyperDrive (HD) is a series of RAM-based solid-state drives invented by Accelerated Logic B.V. employee Pascal Bancsi, who partnered with the British company HyperOs Systems, who manufactured the retail product. The HyperDrive interfaces with and is recognized by computer systems as a standard hard drive.

In computing, a memory module or RAM stick is a printed circuit board on which memory integrated circuits are mounted. Memory modules permit easy installation and replacement in electronic systems, especially computers such as personal computers, workstations, and servers. The first memory modules were proprietary designs that were specific to a model of computer from a specific manufacturer. Later, memory modules were standardized by organizations such as JEDEC and could be used in any system designed to use them.

The Socket G3 Memory Extender (G3MX) was a planned Advanced Micro Devices' solution to the problem of connecting large amounts of memory to a single microprocessor. The G3MX was expected to be available on AMD 800S series chipset for server market starting from 2009, but was officially cancelled together with the cancellation of Socket G3 in early 2008.

Double Data Rate 4 Synchronous Dynamic Random-Access Memory is a type of synchronous dynamic random-access memory with a high bandwidth interface.

A memory rank is a set of DRAM chips connected to the same chip select, which are therefore accessed simultaneously. In practice all DRAM chips share all of the other command and control signals, and only the chip select pins for each rank are separate.

Netlist Inc. is a multinational company headquartered in Irvine, California that designs, manufactures and sells high-performance SSDs and modular memory subsystems to enterprise customers in diverse industries. It also manufactures a line of specialty and legacy memory products to storage customers, appliance customers, system builders and cloud and datacenter customers. Netlist holds a portfolio of patents in the areas of server memory, hybrid memory, storage class memory, rank multiplication and load reduction. Netlist has more than 80 employees and an annual revenue of US $47.2 million as of 2020 The stock was added to NASDAQ in late 2006. In the initial public offering of its common stock in 2006, Netlist sold 6,250,000 shares at $7.00 each. On September 26, 2018, Netlist announced they were moving from NASDAQ and currently trades on the OTCQB.

Double Data Rate 5 Synchronous Dynamic Random-Access Memory is a type of synchronous dynamic random-access memory. Compared to its predecessor DDR4 SDRAM, DDR5 was planned to reduce power consumption, while doubling bandwidth. The standard, originally targeted for 2018, was released on 14 July 2020.

References

- ↑ "HyperCloud Achieves Server Memory Speed Breakthrough at SC11". Cirrascale. November 15, 2011. Archived from the original on January 21, 2012.

- 1 2 "HCDIMM Outperforms LRDIMM in Big Data and Big Memory, CMTL" (PDF). CMTL. Archived from the original (PDF) on 2012-04-25.

- ↑ "Netlist puffs HyperCloud DDR3 memory to 32GB". The Register .