SPI-3 or System Packet Interface Level 3 is the name of a chip-to-chip, channelized, packet interface widely used in high-speed communications devices. It was proposed by PMC-Sierra based on their PL-3 interface to the Optical Internetworking Forum and adopted in June 2000. PL-3 was developed by PMC-Sierra in conjunction with the SATURN Development Group.

It was designed to be used in systems that support OC-48 SONET interfaces . A typical application of SPI-3 is to connect a framer device to a network processor. It has been widely adopted by the high speed networking marketplace.

The interface consists of (per direction):

There are several clocking options. The interface operates around 100 MHz. Implementations of SPI-3 (PL-3) have been produced which allow somewhat higher clock rates. This is important when overhead bytes are added to incoming packets.

SPI-3 (and PL-3) was a highly successful interface with many semiconductor devices produced to it.

Universal Serial Bus (USB) is an industry standard that establishes specifications for cables, connectors and protocols for connection, communication and power supply (interfacing) between computers, peripherals and other computers. A broad variety of USB hardware exists, including 14 different connector types, of which USB-C is the most recent.

Transistor–transistor logic (TTL) is a logic family built from bipolar junction transistors. Its name signifies that transistors perform both the logic function and the amplifying function, as opposed to resistor–transistor logic (RTL) or diode–transistor logic (DTL).

In the seven-layer OSI model of computer networking, the physical layer or layer 1 is the first and lowest layer; The layer most closely associated with the physical connection between devices. This layer may be implemented by a PHY chip.

AVR is a family of microcontrollers developed since 1996 by Atmel, acquired by Microchip Technology in 2016. These are modified Harvard architecture 8-bit RISC single-chip microcontrollers. AVR was one of the first microcontroller families to use on-chip flash memory for program storage, as opposed to one-time programmable ROM, EPROM, or EEPROM used by other microcontrollers at the time.

HyperTransport (HT), formerly known as Lightning Data Transport (LDT), is a technology for interconnection of computer processors. It is a bidirectional serial/parallel high-bandwidth, low-latency point-to-point link that was introduced on April 2, 2001. The HyperTransport Consortium is in charge of promoting and developing HyperTransport technology.

The Serial Peripheral Interface (SPI) is a synchronous serial communication interface specification used for short-distance communication, primarily in embedded systems. The interface was developed by Motorola in the mid-1980s and has become a de facto standard. Typical applications include Secure Digital cards and liquid crystal displays.

In computer engineering, a logic family is one of two related concepts:

Packet over SONET/SDH, abbreviated POS, is a communications protocol for transmitting packets in the form of the Point to Point Protocol (PPP) over SDH or SONET, which are both standard protocols for communicating digital information using lasers or light emitting diodes (LEDs) over optical fibre at high line rates. POS is defined by RFC 2615 as PPP over SONET/SDH. PPP is the Point to Point Protocol that was designed as a standard method of communicating over point-to-point links. Since SONET/SDH uses point-to-point circuits, PPP is well suited for use over these links. Scrambling is performed during insertion of the PPP packets into the SONET/SDH frame to solve various security attacks including denial-of-service attacks and the imitation of SONET/SDH alarms. This modification was justified as cost-effective because the scrambling algorithm was already used by the standard used to transport ATM cells over SONET/SDH. However, scrambling can optionally be disabled to allow a node to be compatible with another node that uses the now obsoleted RFC 1619 version of Packet over SONET/SDH which lacks the scrambler.

The media-independent interface (MII) was originally defined as a standard interface to connect a Fast Ethernet media access control (MAC) block to a PHY chip. The MII is standardized by IEEE 802.3u and connects different types of PHYs to MACs. Being media independent means that different types of PHY devices for connecting to different media can be used without redesigning or replacing the MAC hardware. Thus any MAC may be used with any PHY, independent of the network signal transmission media.

The Optical Internetworking Forum (OIF) is a prominent non-profit consortium that was founded in 1998. It promotes the development and deployment of interoperable computer networking products and services through implementation agreements (IAs) for optical networking products and component technologies including SerDes devices.

The System Packet Interface (SPI) family of Interoperability Agreements from the Optical Internetworking Forum specify chip-to-chip, channelized, packet interfaces commonly used in synchronous optical networking and Ethernet applications. A typical application of such a packet level interface is between a framer or a MAC and a network processor. Another application of this interface might be between a packet processor ASIC and a traffic manager device.

SPI-4.2 is a version of the System Packet Interface published by the Optical Internetworking Forum. It was designed to be used in systems that support OC-192 SONET interfaces and is sometimes used in 10 Gigabit Ethernet based systems.

PL-4 or POS-PHY Level 4 was the name of the interface that the interface SPI-4.2 is based on. It was proposed by PMC-Sierra to the Optical Internetworking Forum. The name means Packet Over SONET Physical layer level 4. PL-4 was developed by PMC-Sierra in conjunction with the Saturn Development Group.

PL-3 or POS-PHY Level 3 is a network protocol. It is the name of the interface that the Optical Internetworking Forum's SPI-3 Interoperability Agreement is based on. It was proposed by PMC-Sierra to the Optical Internetworking Forum and adopted in June 2000. The name means Packet Over SONET Physical layer level 3. PL-3 was developed by PMC-Sierra in conjunction with the SATURN Development Group.

Parallel SCSI is the earliest of the interface implementations in the SCSI family. SPI is a parallel bus; there is one set of electrical connections stretching from one end of the SCSI bus to the other. A SCSI device attaches to the bus but does not interrupt it. Both ends of the bus must be terminated.

VLYNQ is a proprietary interface developed by Texas Instruments and used for broadband products, such as WLAN and modems, VOIP processors and audio and digital media processor chips. The chip implements a full-duplex serial communications interface that enables the extension of an internal bus segment to one or more external physical devices. The external devices are mapped into local, physical address space and appear as if they are on the internal bus. Multiple VLYNQ devices are daisy-chained, communication is peer-to-peer, host/peripheral. Data transferred over the VLYNQ interface is 8B/10B encoded and packetized.

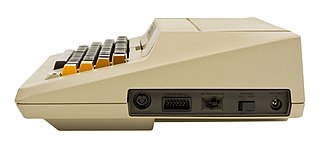

The Serial Input/Output system, universally known as SIO, was a proprietary peripheral bus and related software protocol stacks used on the Atari 8-bit family to provide most input/output duties for those computers. Unlike most I/O systems of the era, such as RS-232, SIO included a lightweight protocol that allowed multiple devices to be attached to a single daisy-chained port that supported dozens of devices. It also supported plug-and-play operations. SIO's designer, Joe Decuir, credits his work on the system as the basis of USB.

V-by-One HS is an electrical digital signaling standard that can run at faster speeds over inexpensive twisted-pair copper cables than Low-voltage differential signaling, or LVDS. It was originally developed by THine Electronics, Inc. in 2007 for high-definition televisions but since 2010 V-by-One HS has been widely adopted in various markets such as document processing, automotive infotainment systems, industrial cameras and machine vision, robotics and amusement equipments.

The Common Electrical I/O (CEI) refers to a series of influential Interoperability Agreements (IAs) that have been published by the Optical Internetworking Forum (OIF). CEI defines the electrical and jitter requirements for 3.125, 6, 11, 25-28, and 56 Gbit/s electrical interfaces.