Related Research Articles

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing – hence the term field-programmable. The FPGA configuration is generally specified using a hardware description language (HDL), similar to that used for an application-specific integrated circuit (ASIC). Circuit diagrams were previously used to specify the configuration, but this is increasingly rare due to the advent of electronic design automation tools.

A CubeSat is a class of miniaturized satellite based around a form factor consisting of 10 cm (3.9 in) cubes. CubeSats have a mass of no more than 2 kg (4.4 lb) per unit, and often use commercial off-the-shelf (COTS) components for their electronics and structure. CubeSats are put into orbit by deployers on the International Space Station, or launched as secondary payloads on a launch vehicle. As of August 2021, more than 1,600 CubeSats have been launched.

Xilinx, Inc. is an American technology and semiconductor company that primarily supplied programmable logic devices. The company was known for inventing the first commercially viable field-programmable gate array (FPGA) and creating the first fabless manufacturing model.

LEON is a radiation-tolerant 32-bit central processing unit (CPU) microprocessor core that implements the SPARC V8 instruction set architecture (ISA) developed by Sun Microsystems. It was originally designed by the European Space Research and Technology Centre (ESTEC), part of the European Space Agency (ESA), without any involvement by Sun. Later versions have been designed by Gaisler Research, under a variety of owners. It is described in synthesizable VHSIC Hardware Description Language (VHDL). LEON has a dual license model: An GNU Lesser General Public License (LGPL) and GNU General Public License (GPL) free and open-source software (FOSS) license that can be used without licensing fee, or a proprietary license that can be purchased for integration in a proprietary product. The core is configurable through VHDL generics, and is used in system on a chip (SOC) designs both in research and commercial settings.

The interplanetary Internet is a conceived computer network in space, consisting of a set of network nodes that can communicate with each other. These nodes are the planet's orbiters and landers, and the Earth ground stations. For example, the orbiters collect the scientific data from the Curiosity rover on Mars through near-Mars communication links, transmit the data to Earth through direct links from the Mars orbiters to the Earth ground stations, and finally the data routed through Earth's internal internet.

The design of spacecraft covers a broad area, including the design of both robotic spacecraft, and spacecraft for human spaceflight.

A single-event upset (SEU), also known as a single-event error (SEE), is a change of state caused by one single ionizing particle striking a sensitive node in a live micro-electronic device, such as in a microprocessor, semiconductor memory, or power transistors. The state change is a result of the free charge created by ionization in or close to an important node of a logic element. The error in device output or operation caused as a result of the strike is called an SEU or a soft error.

MidSTAR-1 is an artificial satellite produced by the United States Naval Academy Small Satellite Program. It was sponsored by the United States Department of Defense (DoD) Space Test Program (STP), and was launched on March 9, 2007 at 03:10 UTC, aboard an Atlas V expendable launch vehicle from Cape Canaveral Air Force Station. MidSTAR-1 flew along with FalconSat 3, STPSat 1, and CFESat as secondary payloads; the primary payload was Orbital Express.

Space Micro Inc is an American company that designs and manufactures high-reliability space and satellite subsystems. Space Micro focuses on radiation-hardened Single Board Computers, Image Processing Computers, Software Defined Radios, Radio Frequency Transceivers and Transponders, Optical Terminals, Space Cameras, Star Trackers and Sun Sensors.

FedSat was an Australian scientific research satellite launched from Tanegashima Space Center, Japan by a NASDA H-IIA launch vehicle on 14 December 2002. The satellite was developed by the Cooperative Research Centre for Satellite Systems, a cooperative made up of several universities, commercial organisations and government bodies. The ground station was at the Institute for Telecommunications Research, part of the University of South Australia, near Adelaide. Since 2005 it was operated by the Australian Department of Defence.

Aldec, Inc. is a privately owned electronic design automation company based in Henderson, Nevada that provides software and hardware used in creation and verification of digital designs targeting FPGA and ASIC technologies.

The Advanced Research and Global Observation Satellite (ARGOS) was launched on 23 February 1999 carrying nine payloads for research and development missions by nine separate researchers. The mission terminated on 31 July 2003.

The Materials International Space Station Experiment (MISSE) is a series of experiments mounted externally on the International Space Station (ISS) that investigates the effects of long-term exposure of materials to the harsh space environment.

The Operationally Responsive Space Office is a joint initiative of several agencies within the United States Department of Defense (DoD). The "stand up" of the office took place 21 May 2007 at Kirtland Air Force Base. The first director of the ORS Office was Col. Kevin McLaughlin, who was also dual-hatted as commander of the Space Development and Test Wing located at Kirtland. The ORS Office focuses on providing quick-response tactical space-based capabilities to the warfighter utilizing smaller satellites, such as the Tactical Satellite Program and smaller launch vehicles.

SpaceCube is a family of high-performance reconfigurable systems designed for spaceflight applications requiring on-board processing. The SpaceCube was developed by engineers at the NASA Goddard Space Flight Center. The SpaceCube 1.0 system is based on Xilinx's Virtex-4 commercial FPGAs. The debut mission of the SpaceCube 1.0, Hubble Servicing Mission 4, was the first time Xilinx's Virtex-4 FPGAs flew in space.

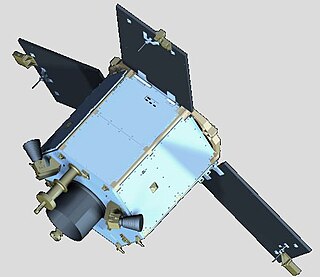

DubaiSat-1 is a remote sensing Earth observation satellite built by the Emirates Institution for Advanced Science and Technology (EIAST) under an agreement with Satrec Initiative, a satellite manufacturing company in South Korea.

Virtex is the flagship family of FPGA products developed by Xilinx, a part of AMD. Other current product lines include Kintex (mid-range) and Artix (low-cost), each including configurations and models optimized for different applications. In addition, Xilinx offers the Spartan low-cost series, which continues to be updated and is nearing production utilizing the same underlying architecture and process node as the larger 7-series devices.

RAX-2 is a CubeSat satellite built as a collaboration between SRI International and students at the University of Michigan College of Engineering. It is the second spacecraft in the RAX mission. The RAX-1 mission ended after approximately two months of operation due to a gradual degradation of the solar panels that ultimately resulted in a loss of power. RAX team members applied the lessons learned from RAX-1 to the design of a second flight unit, RAX-2, which performs the same mission concept of RAX-1 with improved bus performance and additional operational modes. Science measurements are enhanced through interactive experiments with high power ionospheric heaters where FAI will be generated on demand.

A ground segment consists of all the ground-based elements of a space system used by operators and support personnel, as opposed to the space segment and user segment. The ground segment enables management of a spacecraft, and distribution of payload data and telemetry among interested parties on the ground. The primary elements of a ground segment are:

OPTOS was a Spanish nanosatellite designed and developed by INTA with support from the European Cooperation for Space Standardization (ECSS) as a low-cost technology demonstrator. It was launched in 2013 and had a service life of 3 years.

References

- ↑ Surratt, M.; Loomis, H.H.; Ross, A.A.; Duren, R. (2005-03-05). "Challenges of Remote FPGA Configuration for Space Applications". 2005 IEEE Aerospace Conference. Naval Postgraduate School. pp. 1–9. doi:10.1109/AERO.2005.1559549. ISBN 0-7803-8870-4. S2CID 31997734.