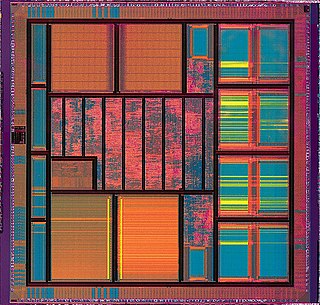

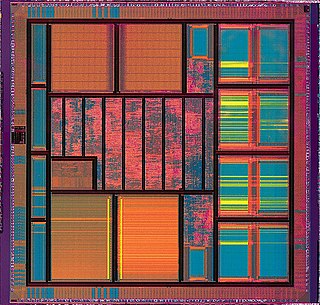

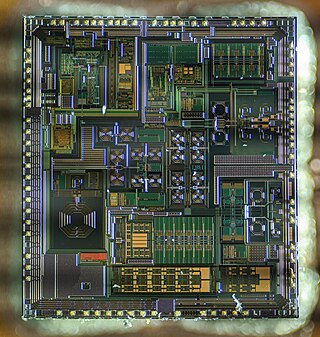

An integrated circuit (IC), also known as a microchip, computer chip, or simply chip, is a small electronic device made up of multiple interconnected electronic components such as transistors, resistors, and capacitors. These components are etched onto a small piece of semiconductor material, usually silicon. Integrated circuits are used in a wide range of electronic devices, including computers, smartphones, and televisions, to perform various functions such as processing and storing information. They have greatly impacted the field of electronics by enabling device miniaturization and enhanced functionality.

Very-large-scale integration (VLSI) is the process of creating an integrated circuit (IC) by combining millions or billions of MOS transistors onto a single chip. VLSI began in the 1970s when MOS integrated circuit chips were developed and then widely adopted, enabling complex semiconductor and telecommunications technologies. The microprocessor and memory chips are VLSI devices.

Complementary metal–oxide–semiconductor is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) fabrication process that uses complementary and symmetrical pairs of p-type and n-type MOSFETs for logic functions. CMOS technology is used for constructing integrated circuit (IC) chips, including microprocessors, microcontrollers, memory chips, and other digital logic circuits. CMOS technology is also used for analog circuits such as image sensors, data converters, RF circuits, and highly integrated transceivers for many types of communication.

SiGe, or silicon–germanium, is an alloy with any molar ratio of silicon and germanium, i.e. with a molecular formula of the form Si1−xGex. It is commonly used as a semiconductor material in integrated circuits (ICs) for heterojunction bipolar transistors or as a strain-inducing layer for CMOS transistors. IBM introduced the technology into mainstream manufacturing in 1989. This relatively new technology offers opportunities in mixed-signal circuit and analog circuit IC design and manufacture. SiGe is also used as a thermoelectric material for high-temperature applications (>700 K).

In computer engineering, a logic family is one of two related concepts:

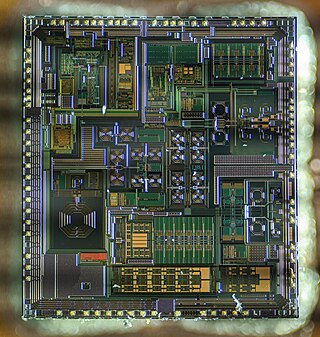

A mixed-signal integrated circuit is any integrated circuit that has both analog circuits and digital circuits on a single semiconductor die. Their usage has grown dramatically with the increased use of cell phones, telecommunications, portable electronics, and automobiles with electronics and digital sensors.

Semiconductor memory is a digital electronic semiconductor device used for digital data storage, such as computer memory. It typically refers to devices in which data is stored within metal–oxide–semiconductor (MOS) memory cells on a silicon integrated circuit memory chip. There are numerous different types using different semiconductor technologies. The two main types of random-access memory (RAM) are static RAM (SRAM), which uses several transistors per memory cell, and dynamic RAM (DRAM), which uses a transistor and a MOS capacitor per cell. Non-volatile memory uses floating-gate memory cells, which consist of a single floating-gate transistor per cell.

In integrated circuits, depletion-load NMOS is a form of digital logic family that uses only a single power supply voltage, unlike earlier NMOS logic families that needed more than one different power supply voltage. Although manufacturing these integrated circuits required additional processing steps, improved switching speed and the elimination of the extra power supply made this logic family the preferred choice for many microprocessors and other logic elements.

Technology computer-aided design is a branch of electronic design automation (EDA) that models semiconductor fabrication and semiconductor device operation. The modeling of the fabrication is termed process TCAD, while the modeling of the device operation is termed device TCAD. Included are the modelling of process steps, and modelling of the behavior of the electrical devices based on fundamental physics, such as the doping profiles of the devices. TCAD may also include the creation of "compact models", which try to capture the electrical behavior of such devices but do not generally derive them from the underlying physics. SPICE simulator itself is usually considered as part of EDA rather than TCAD.

Semiconductor device modeling creates models for the behavior of the electrical devices based on fundamental physics, such as the doping profiles of the devices. It may also include the creation of compact models, which try to capture the electrical behavior of such devices but do not generally derive them from the underlying physics. Normally it starts from the output of a semiconductor process simulation.

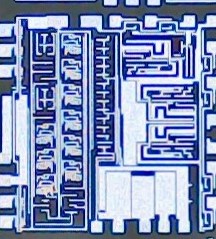

The Electric VLSI Design System is an EDA tool written in the early 1980s by Steven M. Rubin. Electric is used to construct logic wire schematics and to perform analysis of integrated circuit layout. It can also handle hardware description languages such as VHDL and Verilog. The system has many analysis and synthesis tools, including design rule checking, simulation, routing, Layout vs. Schematic, logical effort, and more.

Chih-Tang "Tom" Sah is a Chinese-American electronics engineer and condensed matter physicist. He is best known for inventing CMOS logic with Frank Wanlass at Fairchild Semiconductor in 1963. CMOS is used in nearly all modern very large-scale integration (VLSI) semiconductor devices.

Asad Ali Abidi is a Pakistani-American electrical engineer. He serves as a tenured professor at University of California, Los Angeles, and is the inaugural holder of the Abdus Salam Chair at the Lahore University of Management Sciences (LUMS). He is best known for pioneering RF CMOS technology during the late 1980s to early 1990s. As of 2008, the radio transceivers in all wireless networking devices and modern mobile phones are mass-produced as RF CMOS devices.

Ian A. Young is an Intel engineer. Young is a co-author of 50 research papers, and has 71 patents in switched capacitor circuits, DRAM, SRAM, BiCMOS, x86 clocking, Photonics and spintronics.

The field-effect transistor (FET) is a type of transistor that uses an electric field to control the current through a semiconductor. It comes in two types: junction FET (JFET) and metal-oxide-semiconductor FET (MOSFET). FETs have three terminals: source, gate, and drain. FETs control the current by the application of a voltage to the gate, which in turn alters the conductivity between the drain and source.

Bijan Davari is an Iranian-American electrical engineer. He is an IBM Fellow and Vice President at IBM Thomas J Watson Research Center, Yorktown Hts, NY. His pioneering work in the miniaturization of semiconductor devices changed the world of computing. His research led to the first generation of voltage-scaled deep-submicron CMOS with sufficient performance to totally replace bipolar technology in IBM mainframes and enable new high-performance UNIX servers. As head of IBM’s Semiconductor Research Center (SRDC), he led IBM into the use of Copper interconnect, silicon on insulator (SOI), and Embedded DRAM before its rivals. He is a member of the U.S. National Academy of Engineering and is known for his seminal contributions to the field of CMOS technology. He is an IEEE Fellow, recipient of the J J Ebers Award in 2005 and IEEE Andrew S. Grove Award in 2010. At the present time, he leads the Next Generation Systems Area of research.

RF CMOS is a metal–oxide–semiconductor (MOS) integrated circuit (IC) technology that integrates radio-frequency (RF), analog and digital electronics on a mixed-signal CMOS RF circuit chip. It is widely used in modern wireless telecommunications, such as cellular networks, Bluetooth, Wi-Fi, GPS receivers, broadcasting, vehicular communication systems, and the radio transceivers in all modern mobile phones and wireless networking devices. RF CMOS technology was pioneered by Pakistani engineer Asad Ali Abidi at UCLA during the late 1980s to early 1990s, and helped bring about the wireless revolution with the introduction of digital signal processing in wireless communications. The development and design of RF CMOS devices was enabled by van der Ziel's FET RF noise model, which was published in the early 1960s and remained largely forgotten until the 1990s.

Lawrence Pileggi is the Coraluppi Head and Tanoto Professor of Electrical and Computer Engineering at Carnegie Mellon University. He is a specialist in the automation of integrated circuits, and developing software tools for the optimization of power grids. Pileggi's research has been cited thousands of times in engineering papers.