Related Research Articles

Advanced Micro Devices, Inc. (AMD) is an American multinational corporation and fabless semiconductor company based in Santa Clara, California, that designs, develops and sells computer processors and related technologies for business and consumer markets.

PowerPC is a reduced instruction set computer (RISC) instruction set architecture (ISA) created by the 1991 Apple–IBM–Motorola alliance, known as AIM. PowerPC, as an evolving instruction set, has been named Power ISA since 2006, while the old name lives on as a trademark for some implementations of Power Architecture–based processors.

In electronics and computer science, a reduced instruction set computer (RISC) is a computer architecture designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a complex instruction set computer (CISC), a RISC computer might require more instructions in order to accomplish a task because the individual instructions are written in simpler code. The goal is to offset the need to process more instructions by increasing the speed of each instruction, in particular by implementing an instruction pipeline, which may be simpler to achieve given simpler instructions.

The Motorola 68000 series is a family of 32-bit complex instruction set computer (CISC) microprocessors. During the 1980s and early 1990s, they were popular in personal computers and workstations and were the primary competitors of Intel's x86 microprocessors. They were best known as the processors used in the early Apple Macintosh, the Sharp X68000, the Commodore Amiga, the Sinclair QL, the Atari ST and Falcon, the Atari Jaguar, the Sega Genesis and Sega CD, the Philips CD-i, the Capcom System I (Arcade), the AT&T UNIX PC, the Tandy Model 16/16B/6000, the Sun Microsystems Sun-1, Sun-2 and Sun-3, the NeXT Computer, NeXTcube, NeXTstation, and NeXTcube Turbo, early Silicon Graphics IRIS workstations, the Aesthedes, computers from MASSCOMP, the Texas Instruments TI-89/TI-92 calculators, the Palm Pilot, the Control Data Corporation CDCNET Device Interface, the VTech Precomputer Unlimited and the Space Shuttle. Although no modern desktop computers are based on processors in the 680x0 series, derivative processors are still widely used in embedded systems.

A workstation is a special computer designed for technical or scientific applications. Intended primarily to be used by a single user, they are commonly connected to a local area network and run multi-user operating systems. The term workstation has been used loosely to refer to everything from a mainframe computer terminal to a PC connected to a network, but the most common form refers to the class of hardware offered by several current and defunct companies such as Sun Microsystems, Silicon Graphics, Apollo Computer, DEC, HP, NeXT, and IBM which powered the 3D computer graphics revolution of the late 1990s.

The PowerPC 7xx is a family of third generation 32-bit PowerPC microprocessors designed and manufactured by IBM and Motorola. This family is called the PowerPC G3 by Apple Computer, which introduced it on November 10, 1997. A number of microprocessors from different vendors have been used under the "PowerPC G3" name. Such designations were applied to Mac computers such as the PowerBook G3, the multicolored iMacs, iBooks and several desktops, including both the Beige and Blue and White Power Macintosh G3s. The low power requirements and small size made the processors ideal for laptops and the name lived out its last days at Apple in the iBook.

The Power Mac G5 is a series of personal computers designed, manufactured, and sold by Apple Computer, Inc. from 2003 to 2006 as part of the Power Mac series. When introduced, it was the most powerful computer in Apple's Macintosh lineup, and was marketed by the company as the world's first 64-bit desktop computer. It was also the first desktop computer from Apple to use an anodized aluminum alloy enclosure, and one of only three computers in Apple's lineup to utilize the PowerPC 970 CPU, the others being the iMac G5 and the Xserve G5.

The IBM RS64 is a family of microprocessors introduced in the mid 1990s, and used in IBM's RS/6000 and AS/400 servers.

The PowerPC 970, PowerPC 970FX, and PowerPC 970MP are 64-bit PowerPC CPUs from IBM introduced in 2002. Apple branded the 970 as PowerPC G5 for its Power Mac G5.

Cell is a 64-bit multi-core microprocessor microarchitecture that combines a general-purpose PowerPC core of modest performance with streamlined coprocessing elements which greatly accelerate multimedia and vector processing applications, as well as many other forms of dedicated computation.

The PowerPC 400 family is a line of 32-bit embedded RISC processor cores based on the PowerPC or Power ISA instruction set architectures. The cores are designed to fit inside specialized applications ranging from system-on-a-chip (SoC) microcontrollers, network appliances, application-specific integrated circuits (ASICs) and field-programmable gate arrays (FPGAs) to set-top boxes, storage devices and supercomputers.

A multi-core processor is a microprocessor on a single integrated circuit with two or more separate processing units, called cores, each of which reads and executes program instructions. The instructions are ordinary CPU instructions but the single processor can run instructions on separate cores at the same time, increasing overall speed for programs that support multithreading or other parallel computing techniques. Manufacturers typically integrate the cores onto a single integrated circuit die or onto multiple dies in a single chip package. The microprocessors currently used in almost all personal computers are multi-core.

The 386SLC is an Intel-licensed version of the 386SX, developed and manufactured by IBM in 1991. It included power-management capabilities and an 8KB internal CPU cache, which enabled it to yield comparable performance to 386DX processors of the same clock speed, which were considerably more expensive. Known inside IBM as "Super Little Chip" for its initials, it was used in the IBM PS/2 35, 40 and 56 Series and in the IBM PS/ValuePoint 325T, but never gained much market share. This was mainly due to an agreement with Intel, in which IBM was not allowed to sell their CPUs if they were not part of a system or upgrade board. It was also marketed as an optional upgrade for 8086-equipped IBM PS/2 25 Series computers.

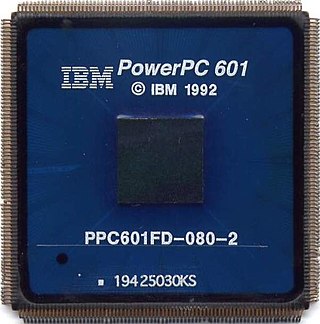

The PowerPC 600 family was the first family of PowerPC processors built. They were designed at the Somerset facility in Austin, Texas, jointly funded and staffed by engineers from IBM and Motorola as a part of the AIM alliance. Somerset was opened in 1992 and its goal was to make the first PowerPC processor and then keep designing general purpose PowerPC processors for personal computers. The first incarnation became the PowerPC 601 in 1993, and the second generation soon followed with the PowerPC 603, PowerPC 604 and the 64-bit PowerPC 620.

Tensilica Inc. was a company based in Silicon Valley in the semiconductor intellectual property core business. It is now a part of Cadence Design Systems.

CoreConnect is a microprocessor bus-architecture from IBM for system-on-a-chip (SoC) designs. It was designed to ease the integration and reuse of processor, system, and peripheral cores within standard and custom SoC designs. As a standard SoC design point, it serves as the foundation of IBM or non-IBM devices. Elements of this architecture include the processor local bus (PLB), the on-chip peripheral bus (OPB), a bus bridge, and a device control register (DCR) bus. High-performance peripherals connect to the high-bandwidth, low-latency PLB. Slower peripheral cores connect to the OPB, which reduces traffic on the PLB. CoreConnect has bridging capabilities to the competing AMBA bus architecture, allowing reuse of existing SoC-components.

Zero ASIC Corporation, formerly Adapteva, Inc., is a fabless semiconductor company focusing on low power many core microprocessor design. The company was the second company to announce a design with 1,000 specialized processing cores on a single integrated circuit.

IBM Power microprocessors are designed and sold by IBM for servers and supercomputers. The name "POWER" was originally presented as an acronym for "Performance Optimization With Enhanced RISC". The Power line of microprocessors has been used in IBM's RS/6000, AS/400, pSeries, iSeries, System p, System i, and Power Systems lines of servers and supercomputers. They have also been used in data storage devices and workstations by IBM and by other server manufacturers like Bull and Hitachi.

References

- 1 2 "Rapport - WikiChip". en.wikichip.org. Retrieved 2020-09-09.

- ↑ "Rapport inc". Archived from the original on 20 December 2007.

- ↑ Tom's hardware: "IBM says Kilocore technology will outrun today's mobile processors" 2006

- ↑ "Rapport Completes Growth Round Funding of $18.5 Million". www.businesswire.com. 2007-10-23. Retrieved 2020-09-09.