Multics is an influential early time-sharing operating system based on the concept of a single-level memory. Nathan Gregory writes that Multics "has influenced all modern operating systems since, from microcomputers to mainframes."

The IBM System/360 (S/360) is a family of mainframe computer systems that was announced by IBM on April 7, 1964, and delivered between 1965 and 1978. It was the first family of computers designed to cover both commercial and scientific applications and a complete range of applications from small to large. The design distinguished between architecture and implementation, allowing IBM to release a suite of compatible designs at different prices. All but the only partially compatible Model 44 and the most expensive systems use microcode to implement the instruction set, featuring 8-bit byte addressing and binary, decimal and hexadecimal floating-point calculations.

The GE 645 mainframe computer was a development of the GE 635 for use in the Multics project. This was the first computer that implemented a configurable hardware protected memory system. It was designed to satisfy the requirements of Project MAC to develop a platform that would host their proposed next generation time-sharing operating system (Multics) and to meet the requirements of a theorized computer utility. The system was the first truly symmetric multiprocessing machine to use virtual memory, it was also among the first machines to implement what is now know as a translation lookaside buffer. The foundational patent for which was granted to John Couleur and Edward Glaser.

The GE-600 series was a family of 36-bit mainframe computers originating in the 1960s, built by General Electric (GE). When GE left the mainframe business the line was sold to Honeywell, which built similar systems into the 1990s as the division moved to Groupe Bull and then NEC.

The CDC 6600 was the flagship of the 6000 series of mainframe computer systems manufactured by Control Data Corporation. Generally considered to be the first successful supercomputer, it outperformed the industry's prior recordholder, the IBM 7030 Stretch, by a factor of three. With performance of up to three megaFLOPS, the CDC 6600 was the world's fastest computer from 1964 to 1969, when it relinquished that status to its successor, the CDC 7600.

The IBM 1401 is a variable-wordlength decimal computer that was announced by IBM on October 5, 1959. The first member of the highly successful IBM 1400 series, it was aimed at replacing unit record equipment for processing data stored on punched cards and at providing peripheral services for larger computers. The 1401 is considered by IBM to be the Ford Model-T of the computer industry due to its mass appeal. Over 12,000 units were produced and many were leased or resold after they were replaced with newer technology. The 1401 was withdrawn on February 8, 1971.

General Comprehensive Operating System is a family of operating systems oriented toward the 36-bit GE-600 series and Honeywell 6000 series mainframe computers.

Addressing modes are an aspect of the instruction set architecture in most central processing unit (CPU) designs. The various addressing modes that are defined in a given instruction set architecture define how the machine language instructions in that architecture identify the operand(s) of each instruction. An addressing mode specifies how to calculate the effective memory address of an operand by using information held in registers and/or constants contained within a machine instruction or elsewhere.

The IBM 1400 series were second-generation (transistor) mid-range business decimal computers that IBM marketed in the early 1960s. The computers were offered to replace tabulating machines like the IBM 407. The 1400-series machines stored information in magnetic cores as variable-length character strings separated on the left by a special bit, called a "wordmark," and on the right by a "record mark." Arithmetic was performed digit-by-digit. Input and output support included punched card, magnetic tape, and high-speed line printers. Disk storage was also available.

In computer architecture, 36-bit integers, memory addresses, or other data units are those that are 36 bits wide. Also, 36-bit central processing unit (CPU) and arithmetic logic unit (ALU) architectures are those that are based on registers, address buses, or data buses of that size. 36-bit computers were popular in the early mainframe computer era from the 1950s through the early 1970s.

Byte addressing in hardware architectures supports accessing individual bytes. Computers with byte addressing are sometimes called byte machines, in contrast to word-addressable architectures, word machines, that access data by word.

The Burroughs B2500 through Burroughs B4900 was a series of mainframe computers developed and manufactured by Burroughs Corporation in Pasadena, California, United States, from 1966 to 1991. They were aimed at the business world with an instruction set optimized for the COBOL programming language. They were also known as Burroughs Medium Systems, by contrast with the Burroughs Large Systems and Burroughs Small Systems.

The Honeywell 200 was a character-oriented two-address commercial computer introduced by Honeywell in December 1963, the basis of later models in Honeywell 200 Series, including 1200, 1250, 2200, 3200, 4200 and others, and the character processor of the Honeywell 8200 (1968).

The CDC 3000 series are a family of mainframe computers from Control Data Corporation (CDC). The first member, the CDC 3600, was a 48-bit system introduced in 1963. The same basic design led to the cut-down CDC 3400 of 1964, and then the 24-bit CDC 3300, 3200 and 3100 introduced between 1964 and 1965. The 3000 series replaced the earlier CDC 1604 and CDC 924 systems.

The CDC 6000 series is a discontinued family of mainframe computers manufactured by Control Data Corporation in the 1960s. It consisted of the CDC 6200, CDC 6300, CDC 6400, CDC 6500, CDC 6600 and CDC 6700 computers, which were all extremely rapid and efficient for their time. Each is a large, solid-state, general-purpose, digital computer that performs scientific and business data processing as well as multiprogramming, multiprocessing, Remote Job Entry, time-sharing, and data management tasks under the control of the operating system called SCOPE. By 1970 there also was a time-sharing oriented operating system named KRONOS. They were part of the first generation of supercomputers. The 6600 was the flagship of Control Data's 6000 series.

The SDS Sigma series is a series of third generation computers that were introduced by Scientific Data Systems of the United States in 1966. The first machines in the series are the 16-bit Sigma 2 and the 32-bit Sigma 7; the Sigma 7 was the first 32-bit computer released by SDS. At the time, the only competition for the Sigma 7 was the IBM 360.

The PDP-11 architecture is a 16-bit CISC instruction set architecture (ISA) developed by Digital Equipment Corporation (DEC). It is implemented by central processing units (CPUs) and microprocessors used in PDP-11 minicomputers. It was in wide use during the 1970s, but was eventually overshadowed by the more powerful VAX architecture in the 1980s.

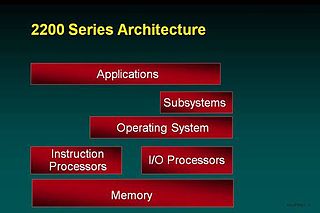

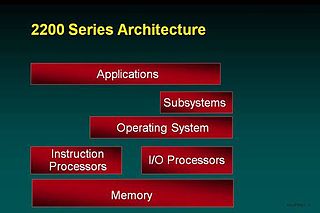

The figure shows a high-level architecture of the OS 2200 system identifying major hardware and software components. The majority of the Unisys software is included in the subsystems and applications area of the model. For example, the database managers are subsystems and the compilers are applications.

The DATANET-30, or DN-30 for short, was a computer manufactured by General Electric designed in 1961-1963 to be used as a communications computer. It was later used as a front-end processor for data communications. It became the first front end communications computer. The names on the patent were Don Birmingham, Bob McKenzie, Bud Pine, and Bill Hill.

The 12-bit ND812, produced by Nuclear Data, Inc., was a commercial minicomputer developed for the scientific computing market. Nuclear Data introduced it in 1970 at a price under $10,000.