The Extended Industry Standard Architecture is a bus standard for IBM PC compatible computers. It was announced in September 1988 by a consortium of PC clone vendors as an alternative to IBM's proprietary Micro Channel architecture (MCA) in its PS/2 series.

Industry Standard Architecture (ISA) is the 16-bit internal bus of IBM PC/AT and similar computers based on the Intel 80286 and its immediate successors during the 1980s. The bus was (largely) backward compatible with the 8-bit bus of the 8088-based IBM PC, including the IBM PC/XT as well as IBM PC compatibles.

The Intel 486, officially named i486 and also known as 80486, is a higher-performance follow-up to the Intel 386 microprocessor. The i486 was introduced in 1989 and was the first tightly pipelined x86 design as well as the first x86 chip to use more than a million transistors, due to a large on-chip cache and an integrated floating-point unit. It represents a fourth generation of binary compatible CPUs since the original 8086 of 1978.

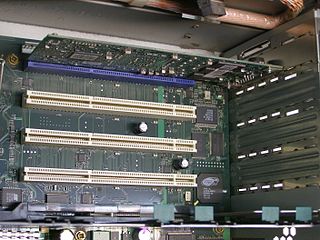

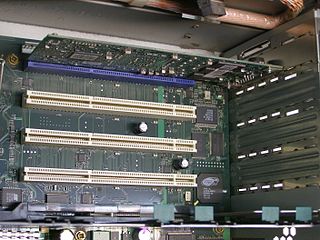

Peripheral Component Interconnect (PCI) is a local computer bus for attaching hardware devices in a computer and is part of the PCI Local Bus standard. The PCI bus supports the functions found on a processor bus but in a standardized format that is independent of any given processor's native bus. Devices connected to the PCI bus appear to a bus master to be connected directly to its own bus and are assigned addresses in the processor's address space. It is a parallel bus, synchronous to a single bus clock. Attached devices can take either the form of an integrated circuit fitted onto the motherboard or an expansion card that fits into a slot. The PCI Local Bus was first implemented in IBM PC compatibles, where it displaced the combination of several slow Industry Standard Architecture (ISA) slots and one fast VESA Local Bus (VLB) slot as the bus configuration. It has subsequently been adopted for other computer types. Typical PCI cards used in PCs include: network cards, sound cards, modems, extra ports such as Universal Serial Bus (USB) or serial, TV tuner cards and hard disk drive host adapters. PCI video cards replaced ISA and VLB cards until rising bandwidth needs outgrew the abilities of PCI. The preferred interface for video cards then became Accelerated Graphics Port (AGP), a superset of PCI, before giving way to PCI Express.

The VESA Local Bus is a short-lived expansion bus introduced during the i486 generation of x86 IBM-compatible personal computers. Created by VESA, the VESA Local Bus worked alongside the then-dominant ISA bus to provide a standardized high-speed conduit intended primarily to accelerate video (graphics) operations. VLB provides a standardized fast path that add-in (video) card makers could tap for greatly accelerated memory-mapped I/O and DMA, while still using the familiar ISA bus to handle basic device duties such as interrupts and port-mapped I/O.

Direct memory access (DMA) is a feature of computer systems that allows certain hardware subsystems to access main system memory independently of the central processing unit (CPU).

NuBus is a 32-bit parallel computer bus, originally developed at MIT and standardized in 1987 as a part of the NuMachine workstation project. The first complete implementation of the NuBus was done by Western Digital for their NuMachine, and for the Lisp Machines Inc. LMI Lambda. The NuBus was later incorporated in Lisp products by Texas Instruments (Explorer), and used as the main expansion bus by Apple Computer and a variant called NeXTBus was developed by NeXT. It is no longer widely used outside the embedded market.

Micro Channel architecture, or the Micro Channel bus, was a proprietary 16- or 32-bit parallel computer bus introduced by IBM in 1987 which was used on PS/2 and other computers until the mid-1990s. Its name is commonly abbreviated as "MCA", although not by IBM. In IBM products, it superseded the ISA bus and was itself subsequently superseded by the PCI bus architecture.

A SCSI host adapter is a device used to connect one or more other SCSI devices to a computer bus. It is commonly called a SCSI controller, which is not strictly correct as any component understanding the SCSI protocol can be called a controller. In this sense all SCSI devices have a SCSI controller built into them, while host adapters bear responsibility for transferring data between the SCSI bus and the computer's input/output bus. SCSI adapters serve as a worthy adapter for FireWire Ports.

The SGI Indigo2 and the SGI Challenge M are Unix workstations which were designed and sold by SGI from 1992 to 1997.

Octane series of IRIX workstations was developed and sold by SGI in the 2000s. Octane and Octane2 are two-way multiprocessing-capable workstations, originally based on the MIPS Technologies R10000 microprocessor. Newer Octanes are based on the R12000 and R14000. The Octane2 has four improvements: a revised power supply, system board, and Xbow ASIC. The Octane2 has VPro graphics and supports all the VPro cards. Later revisions of the Octane include some of the improvements introduced in the Octane2. The codenames for the Octane and Octane2 are "Racer" and "Speedracer" respectively.

PCI-X, short for Peripheral Component Interconnect eXtended, is a computer bus and expansion card standard that enhances the 32-bit PCI local bus for higher bandwidth demanded mostly by servers and workstations. It uses a modified protocol to support higher clock speeds, but is otherwise similar in electrical implementation. PCI-X 2.0 added speeds up to 533 MHz, with a reduction in electrical signal levels.

XIO is a packet-based, high-performance computer bus employed by the SGI Origin 2000, Octane, Altix, Fuel and Tezro machines. The XIO forms a bus between high-performance system devices and the memory controller.

The Indigo, introduced as the IRIS Indigo, is a line of workstation computers developed and manufactured by Silicon Graphics, Inc. (SGI). SGI first announced the system in July 1991.

Multibus is a computer bus standard used in industrial systems. It was developed by Intel Corporation and was adopted as the IEEE 796 bus.

The feature connector was an internal connector found mostly in some older ISA, VESA Local Bus, and PCI graphics cards, but also on some early AGP ones. It was intended for use by devices which needed to exchange large amounts of data with the graphics card without hogging a computer system's CPU or data bus, such as TV tuner cards, video capture cards, MPEG video decoders, and first generation 3D graphic accelerator cards. Early examples include the IBM EGA video adapter.

Released as the expansion bus of the Commodore Amiga 3000 in 1990, the Zorro III computer bus was used to attach peripheral devices to an Amiga motherboard. Designed by Commodore International lead engineer Dave Haynie, the 32-bit Zorro III replaced the 16-bit Zorro II bus used in the Amiga 2000. As with the Zorro II bus, Zorro III allowed for true Plug and Play autodetection wherein devices were dynamically allocated the resources they needed on boot.

The R10000, code-named "T5", is a RISC microprocessor implementation of the MIPS IV instruction set architecture (ISA) developed by MIPS Technologies, Inc. (MTI), then a division of Silicon Graphics, Inc. (SGI). The chief designers are Chris Rowen and Kenneth C. Yeager. The R10000 microarchitecture is known as ANDES, an abbreviation for Architecture with Non-sequential Dynamic Execution Scheduling. The R10000 largely replaces the R8000 in the high-end and the R4400 elsewhere. MTI was a fabless semiconductor company; the R10000 was fabricated by NEC and Toshiba. Previous fabricators of MIPS microprocessors such as Integrated Device Technology (IDT) and three others did not fabricate the R10000 as it was more expensive to do so than the R4000 and R4400.

The R5000 is a 64-bit, little endian (mipsel) superscalar, in-order execution 2-issue design microprocessor, that implements the MIPS IV instruction set architecture (ISA) developed by Quantum Effect Design (QED) in 1996. The project was funded by MIPS Technologies, Inc (MTI), also the licensor. MTI then licensed the design to Integrated Device Technology (IDT), NEC, NKK, and Toshiba. The R5000 succeeded the QED R4600 and R4700 as their flagship high-end embedded microprocessor. IDT marketed its version of the R5000 as the 79RV5000, NEC as VR5000, NKK as the NR5000, and Toshiba as the TX5000. The R5000 was sold to PMC-Sierra when the company acquired QED. Derivatives of the R5000 are still in production today for embedded systems.

Since 1985, many processors implementing some version of the MIPS architecture have been designed and used widely.