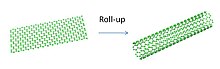

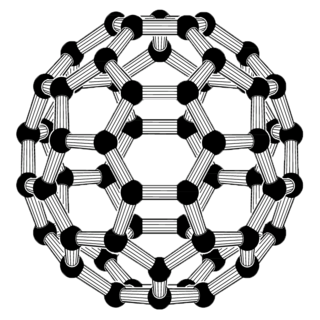

A carbon nanotube (CNT) is a tube made of carbon with a diameter in the nanometre range (nanoscale). They are one of the allotropes of carbon.

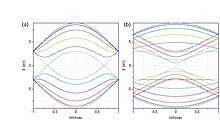

A Schottky barrier, named after Walter H. Schottky, is a potential energy barrier for electrons formed at a metal–semiconductor junction. Schottky barriers have rectifying characteristics, suitable for use as a diode. One of the primary characteristics of a Schottky barrier is the Schottky barrier height, denoted by ΦB. The value of ΦB depends on the combination of metal and semiconductor.

In solid-state physics, the electron mobility characterises how quickly an electron can move through a metal or semiconductor when pulled by an electric field. There is an analogous quantity for holes, called hole mobility. The term carrier mobility refers in general to both electron and hole mobility.

Nanoelectromechanical systems (NEMS) are a class of devices integrating electrical and mechanical functionality on the nanoscale. NEMS form the next logical miniaturization step from so-called microelectromechanical systems, or MEMS devices. NEMS typically integrate transistor-like nanoelectronics with mechanical actuators, pumps, or motors, and may thereby form physical, biological, and chemical sensors. The name derives from typical device dimensions in the nanometer range, leading to low mass, high mechanical resonance frequencies, potentially large quantum mechanical effects such as zero point motion, and a high surface-to-volume ratio useful for surface-based sensing mechanisms. Applications include accelerometers and sensors to detect chemical substances in the air.

The threshold voltage, commonly abbreviated as Vth or VGS(th), of a field-effect transistor (FET) is the minimum gate-to-source voltage (VGS) that is needed to create a conducting path between the source and drain terminals. It is an important scaling factor to maintain power efficiency.

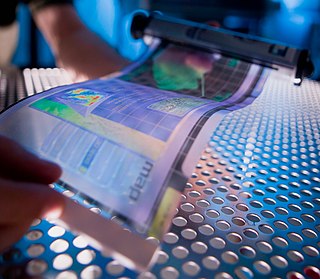

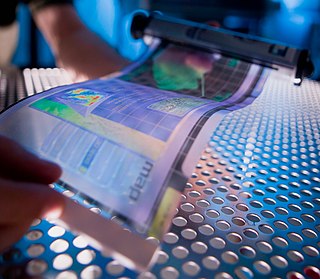

An organic field-effect transistor (OFET) is a field-effect transistor using an organic semiconductor in its channel. OFETs can be prepared either by vacuum evaporation of small molecules, by solution-casting of polymers or small molecules, or by mechanical transfer of a peeled single-crystalline organic layer onto a substrate. These devices have been developed to realize low-cost, large-area electronic products and biodegradable electronics. OFETs have been fabricated with various device geometries. The most commonly used device geometry is bottom gate with top drain and source electrodes, because this geometry is similar to the thin-film silicon transistor (TFT) using thermally grown SiO2 as gate dielectric. Organic polymers, such as poly(methyl-methacrylate) (PMMA), can also be used as dielectric. One of the benefits of OFETs, especially compared with inorganic TFTs, is their unprecedented physical flexibility, which leads to biocompatible applications, for instance in the future health care industry of personalized biomedicines and bioelectronics.

Phaedon Avouris is a Greek chemical physicist and materials scientist. He is an IBM Fellow and was formerly the group leader for Nanometer Scale Science and Technology at the Thomas J. Watson Research Center in Yorktown Heights, New York.

Hybrid solar cells combine advantages of both organic and inorganic semiconductors. Hybrid photovoltaics have organic materials that consist of conjugated polymers that absorb light as the donor and transport holes. Inorganic materials in hybrid cells are used as the acceptor and electron transporter in the structure. The hybrid photovoltaic devices have a potential for not only low-cost by roll-to-roll processing but also for scalable solar power conversion.

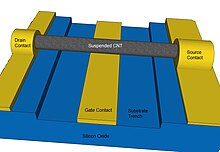

Carbon nanotubes (CNTs) are cylinders of one or more layers of graphene (lattice). Diameters of single-walled carbon nanotubes (SWNTs) and multi-walled carbon nanotubes (MWNTs) are typically 0.8 to 2 nm and 5 to 20 nm, respectively, although MWNT diameters can exceed 100 nm. CNT lengths range from less than 100 nm to 0.5 m.

In solid-state physics, a metal–semiconductor (M–S) junction is a type of electrical junction in which a metal comes in close contact with a semiconductor material. It is the oldest practical semiconductor device. M–S junctions can either be rectifying or non-rectifying. The rectifying metal–semiconductor junction forms a Schottky barrier, making a device known as a Schottky diode, while the non-rectifying junction is called an ohmic contact.

Organic photovoltaic devices (OPVs) are fabricated from thin films of organic semiconductors, such as polymers and small-molecule compounds, and are typically on the order of 100 nm thick. Because polymer based OPVs can be made using a coating process such as spin coating or inkjet printing, they are an attractive option for inexpensively covering large areas as well as flexible plastic surfaces. A promising low cost alternative to conventional solar cells made of crystalline silicon, there is a large amount of research being dedicated throughout industry and academia towards developing OPVs and increasing their power conversion efficiency.

A device generating linear or rotational motion using carbon nanotube(s) as the primary component, is termed a nanotube nanomotor. Nature already has some of the most efficient and powerful kinds of nanomotors. Some of these natural biological nanomotors have been re-engineered to serve desired purposes. However, such biological nanomotors are designed to work in specific environmental conditions. Laboratory-made nanotube nanomotors on the other hand are significantly more robust and can operate in diverse environments including varied frequency, temperature, mediums and chemical environments. The vast differences in the dominant forces and criteria between macroscale and micro/nanoscale offer new avenues to construct tailor-made nanomotors. The various beneficial properties of carbon nanotubes makes them the most attractive material to base such nanomotors on.

NanoIntegris is a nanotechnology company based in Boisbriand, Quebec specializing in the production of enriched, single-walled carbon nanotubes. In 2012, NanoIntegris was acquired by Raymor Industries, a large-scale producer of single-wall carbon nanotubes using the plasma torch process.

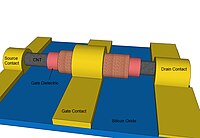

Single-walled carbon nanotubes in the fields of quantum mechanics and nanoelectronics, have the ability to conduct electricity. This conduction can be ballistic, diffusive, or based on scattering. When ballistic in nature conductance can be treated as if the electrons experience no scattering.

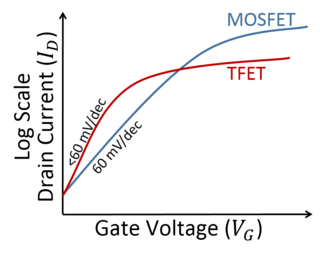

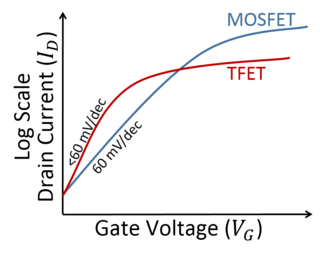

The tunnel field-effect transistor (TFET) is an experimental type of transistor. Even though its structure is very similar to a metal–oxide–semiconductor field-effect transistor (MOSFET), the fundamental switching mechanism differs, making this device a promising candidate for low power electronics. TFETs switch by modulating quantum tunneling through a barrier instead of modulating thermionic emission over a barrier as in traditional MOSFETs. Because of this, TFETs are not limited by the thermal Maxwell–Boltzmann tail of carriers, which limits MOSFET drain current subthreshold swing to about 60 mV/decade of current at room temperature.

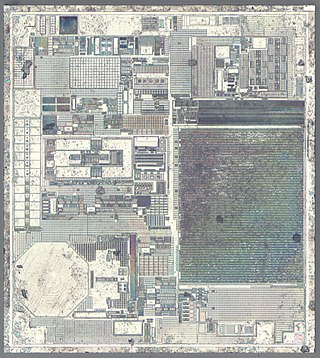

Carbon nanotube computers are a class of experimental computing processors constructed from carbon nanotube field-effect transistors, instead of from conventional silicon-based field-effect transistors.

The field-effect transistor (FET) is a type of transistor that uses an electric field to control the flow of current in a semiconductor. It comes in two types: junction FET (JFET) and metal-oxide-semiconductor FET (MOSFET). FETs have three terminals: source, gate, and drain. FETs control the flow of current by the application of a voltage to the gate, which in turn alters the conductivity between the drain and source.

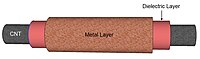

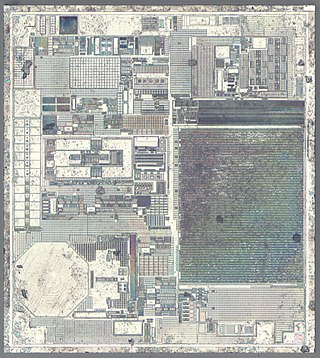

In nanotechnology, carbon nanotube interconnects refer to the proposed use of carbon nanotubes in the interconnects between the elements of an integrated circuit. Carbon nanotubes (CNTs) can be thought of as single atomic layer graphite sheets rolled up to form seamless cylinders. Depending on the direction on which they are rolled, CNTs can be semiconducting or metallic. Metallic carbon nanotubes have been identified as a possible interconnect material for the future technology generations and to replace copper interconnects. Electron transport can go over long nanotube lengths, 1 μm, enabling CNTs to carry very high currents (i.e. up to a current density of 109 A∙cm−2) with essentially no heating due to nearly one dimensional electronic structure. Despite the current saturation in CNTs at high fields, the mitigation of such effects is possible due to encapsulated nanowires.

In materials science, vertically aligned carbon nanotube arrays (VANTAs) are a unique microstructure consisting of carbon nanotubes oriented with their longitudinal axis perpendicular to a substrate surface. These VANTAs effectively preserve and often accentuate the unique anisotropic properties of individual carbon nanotubes and possess a morphology that may be precisely controlled. VANTAs are consequently widely useful in a range of current and potential device applications.

A single-electron transistor (SET) is a sensitive electronic device based on the Coulomb blockade effect. In this device the electrons flow through a tunnel junction between source/drain to a quantum dot. Moreover, the electrical potential of the island can be tuned by a third electrode, known as the gate, which is capacitively coupled to the island. The conductive island is sandwiched between two tunnel junctions modeled by capacitors, and , and resistors, and , in parallel.