Microelectromechanical systems is the technology of microscopic devices, particularly those with moving parts. It merges at the nano-scale into nanoelectromechanical systems (NEMS) and nanotechnology. MEMS are also referred to as micromachines in Japan, or micro systems technology (MST) in Europe.

Semiconductor device fabrication is the process used to create the integrated circuits that are present in everyday electrical and electronic devices. It is a multiple-step sequence of photolithographic and chemical processing steps during which electronic circuits are gradually created on a wafer made of pure semiconducting material. Silicon is almost always used, but various compound semiconductors are used for specialized applications.

In semiconductor technology, copper interconnects are used in silicon integrated circuits (ICs) to reduce propagation delays and power consumption. Since copper is a better conductor than aluminium, ICs using copper for their interconnects can have interconnects with narrower dimensions, and use less energy to pass electricity through them. Together, these effects lead to ICs with better performance. They were first introduced by IBM, with assistance from Motorola, in 1997.

Deep reactive-ion etching (DRIE) is a highly anisotropic etch process used to create deep penetration, steep-sided holes and trenches in wafers/substrates, typically with high aspect ratios. It was developed for microelectromechanical systems (MEMS), which require these features, but is also used to excavate trenches for high-density capacitors for DRAM and more recently for creating through silicon vias (TSVs) in advanced 3D wafer level packaging technology.

Surface finishing is a broad range of industrial processes that alter the surface of a manufactured item to achieve a certain property. Finishing processes may be employed to: improve appearance, adhesion or wettability, solderability, corrosion resistance, tarnish resistance, chemical resistance, wear resistance, hardness, modify electrical conductivity, remove burrs and other surface flaws, and control the surface friction. In limited cases some of these techniques can be used to restore original dimensions to salvage or repair an item. An unfinished surface is often called mill finish.

The front-end-of-line (FEOL) is the first portion of IC fabrication where the individual devices are patterned in the semiconductor. FEOL generally covers everything up to the deposition of metal interconnect layers.

Microfabrication is the process of fabricating miniature structures of micrometre scales and smaller. Historically, the earliest microfabrication processes were used for integrated circuit fabrication, also known as "semiconductor manufacturing" or "semiconductor device fabrication". In the last two decades microelectromechanical systems (MEMS), microsystems, micromachines and their subfields, microfluidics/lab-on-a-chip, optical MEMS, RF MEMS, PowerMEMS, BioMEMS and their extension into nanoscale have re-used, adapted or extended microfabrication methods. Flat-panel displays and solar cells are also using similar techniques.

Etching is used in microfabrication to chemically remove layers from the surface of a wafer during manufacturing. Etching is a critically important process module, and every wafer undergoes many etching steps before it is complete.

LOCOS, short for LOCal Oxidation of Silicon, is a microfabrication process where silicon dioxide is formed in selected areas on a silicon wafer having the Si-SiO2 interface at a lower point than the rest of the silicon surface.

Ultrasonic machining, or strictly speaking the "Ultrasonic vibration machining", is a subtraction manufacturing process that removes material from the surface of a part through high frequency, low amplitude vibrations of a tool against the material surface in the presence of fine abrasive particles. The tool travels vertically or orthogonal to the surface of the part at amplitudes of 0.05 to 0.125 mm. The fine abrasive grains are mixed with water to form a slurry that is distributed across the part and the tip of the tool. Typical grain sizes of the abrasive material range from 100 to 1000, where smaller grains produce smoother surface finishes.

Eco pickled surface (EPS) is a process applied to hot rolled sheet steel to remove all surface oxides and clean the steel surface. Steel which has undergone the EPS process acquires a high degree of resistance to subsequent development of surface oxide (rust), so long as it does not come into direct contact with moisture. EPS was developed by The Material Works, Ltd., which has filed several patent applications covering the process. It is primarily intended to be a replacement of the familiar acid pickling process wherein steel strip is immersed in solutions of hydrochloric and sulfuric acids to chemically remove oxides.

Thermocompression bonding describes a wafer bonding technique and is also referred to as diffusion bonding, pressure joining, thermocompression welding or solid-state welding. Two metals, e.g. gold (Au)-gold (Au), are brought into atomic contact applying force and heat simultaneously. The diffusion requires atomic contact between the surfaces due to the atomic motion. The atoms migrate from one crystal lattice to the other one based on crystal lattice vibration. This atomic interaction sticks the interface together. The diffusion process is described by the following three processes:

Direct bonding, or fusion bonding, describes a wafer bonding process without any additional intermediate layers. The bonding process is based on chemical bonds between two surfaces of any material possible meeting numerous requirements. These requirements are specified for the wafer surface as sufficiently clean, flat and smooth. Otherwise unbonded areas so called voids, i.e. interface bubbles, can occur.

Anodic bonding is a wafer bonding process to seal glass to either silicon or metal without introducing an intermediate layer; it is commonly used to seal glass to silicon wafers in electronics and microfluidics. This bonding technique, also known as field assisted bonding or electrostatic sealing, is mostly used for connecting silicon/glass and metal/glass through electric fields. The requirements for anodic bonding are clean and even wafer surfaces and atomic contact between the bonding substrates through a sufficiently powerful electrostatic field. Also necessary is the use of borosilicate glass containing a high concentration of alkali ions. The coefficient of thermal expansion (CTE) of the processed glass needs to be similar to those of the bonding partner.

Plasma-activated bonding is a derivative, directed to lower processing temperatures for direct bonding with hydrophilic surfaces. The main requirements for lowering temperatures of direct bonding are the use of materials melting at low temperatures and with different coefficients of thermal expansion (CTE).

Eutectic bonding, also referred to as eutectic soldering, describes a wafer bonding technique with an intermediate metal layer that can produce a eutectic system. Those eutectic metals are alloys that transform directly from solid to liquid state, or vice versa from liquid to solid state, at a specific composition and temperature without passing a two-phase equilibrium, i.e. liquid and solid state. The fact that the eutectic temperature can be much lower than the melting temperature of the two or more pure elements can be important in eutectic bonding.

Glass frit bonding, also referred to as glass soldering or seal glass bonding, describes a wafer bonding technique with an intermediate glass layer. It is a widely used encapsulation technology for surface micro-machined structures, e.g., accelerometers or gyroscopes. This technique utilizes low melting glass and therefore provides various advantages including that viscosity of glass decreases with an increase of temperature. The viscous flow of glass has effects to compensate and planarize surface irregularities, convenient for bonding wafers with a high roughness due to plasma etching or deposition. A low viscosity promotes hermetically sealed encapsulation of structures based on a better adaption of the structured shapes. Further, the coefficient of thermal expansion (CTE) of the glass material is adapted to silicon. This results in low stress in the bonded wafer pair.

Photolithography is a process in removing select portions of thin films used in microfabrication. Microfabrication is the production of parts on the micro- and nano- scale, typically on the surface of silicon wafers for the production of microelectromechanical systems (MEMS). Photolithography makes this process possible through the combined use of hexamethyldisilazane (HMDS), photoresist, a spin or spray coater, photomask, an exposure system and other various chemicals. By carefully manipulating these factors it is possible to create nearly any geometry microstructure on the surface of a silicon wafer. The chemical interaction between all the different components and the surface of the silicon wafer makes photolithography an interesting chemistry problem. Current science has been able to create features on the surface of silicon wafers between 1 and 100 µm.

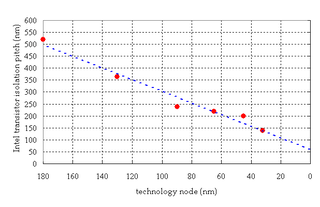

In integrated circuits (ICs), interconnects are structures that connect two or more circuit elements together electrically. The design and layout of interconnects on an IC is vital to its proper function, performance, power efficiency, reliability, and fabrication yield. The material interconnects are made from depends on many factors. Chemical and mechanical compatibility with the semiconductor substrate, and the dielectric in between the levels of interconnect is necessary, otherwise barrier layers are needed. Suitability for fabrication is also required; some chemistries and processes prevent integration of materials and unit processes into a larger technology (recipe) for IC fabrication. In fabrication, interconnects are formed during the back-end-of-line after the fabrication of the transistors on the substrate.