In computer architecture, a bus is a communication system that transfers data between components inside a computer, or between computers. This expression covers all related hardware components and software, including communication protocols.

The 8086 is a 16-bit microprocessor chip designed by Intel between early 1976 and June 8, 1978, when it was released. The Intel 8088, released July 1, 1979, is a slightly modified chip with an external 8-bit data bus, and is notable as the processor used in the original IBM PC design.

Direct memory access (DMA) is a feature of computer systems and allows certain hardware subsystems to access main system memory independently of the central processing unit (CPU).

Chip RAM is a commonly used term for the integrated RAM used in Commodore's line of Amiga computers. Chip RAM is shared between the central processing unit (CPU) and the Amiga's dedicated chipset. It was also, rather misleadingly, known as "graphics RAM".

The transputer is a series of pioneering microprocessors from the 1980s, intended for parallel computing. To support this, each transputer had its own integrated memory and serial communication links to exchange data with other transputers. They were designed and produced by Inmos, a semiconductor company based in Bristol, United Kingdom.

The Intel 8085 ("eighty-eighty-five") is an 8-bit microprocessor produced by Intel and introduced in March 1976. It is software-binary compatible with the more-famous Intel 8080 with only two minor instructions added to support its added interrupt and serial input/output features. However, it requires less support circuitry, allowing simpler and less expensive microcomputer systems to be built.

The Intel 4040 microprocessor was the successor to the Intel 4004. It was introduced in 1974. The 4040 employed a 10 μm silicon gate enhancement load PMOS technology, was made up of 3,000 transistors and could execute approximately 62,000 instructions per second. General performance, bus layout and instruction set was identical to the 4004, with the main improvements being in the addition of extra lines and instructions to recognise and service interrupts and hardware Halt/Stop commands, an extended internal stack and general-purpose "Index" register space to handle nesting of several subroutines and/or interrupts, plus a doubling of program ROM address range.

A front-side bus (FSB) is a computer communication interface (bus) that was often used in Intel-chip-based computers during the 1990s and 2000s. The EV6 bus served the same function for competing AMD CPUs. Both typically carry data between the central processing unit (CPU) and a memory controller hub, known as the northbridge.

The MSP430 is a mixed-signal microcontroller family from Texas Instruments, first introduced on 14 February 1992. Built around a 16-bit CPU, the MSP430 is designed for low cost and, specifically, low power consumption embedded applications.

Memory-mapped I/O (MMIO) and port-mapped I/O (PMIO) are two complementary methods of performing input/output (I/O) between the central processing unit (CPU) and peripheral devices in a computer. An alternative approach is using dedicated I/O processors, commonly known as channels on mainframe computers, which execute their own instructions.

The Atari Falcon030, released in 1992, was the final personal computer product from Atari Corporation. A high-end model of the Atari ST line, the machine is based on a Motorola 68030 CPU and a Motorola 56001 digital signal processor, a feature which distinguishes it from most other microcomputers of the era. It includes a new VIDEL programmable graphics system which greatly improves graphics capabilities.

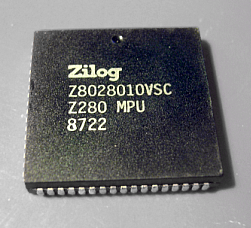

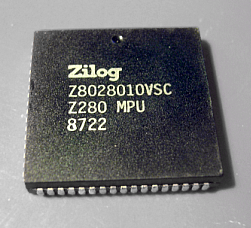

The Zilog Z280 is a 16-bit microprocessor, an enhancement of the Zilog Z80 architecture, introduced in July 1987. It is basically the Z800, renamed, with slight improvements such as being fabricated in CMOS. It was a commercial failure. Zilog added a memory management unit (MMU) to expand the addressing range to 16 MB, features for multitasking and multiprocessor and coprocessor configurations, and 256 bytes of on-chip static RAM, configurable as either a cache for instructions and/or data, or as part of the ordinary address space. It has a huge number of new instructions and addressing modes giving a total of over 2000 combinations. It is capable of efficiently handling 32-bit data operations including hardware multiply, divide, and sign extension. It offers Supervisor and User operating modes, and optionally separate address spaces for instructions and data in both modes. Its internal clock signal can be configured to run at 1, 2 or 4 times the external clock's speed. Unlike the Z80 the Z280 uses a multiplexed arrangement for its address and data busses. More successful extensions of the Z80-architecture include the Hitachi HD64180 in 1986 and Zilog eZ80 in 2001, among others. See further Zilog Z800.

The Blackfin is a family of 16-/32-bit microprocessors developed, manufactured and marketed by Analog Devices. The processors have built-in, fixed-point digital signal processor (DSP) functionality supplied by 16-bit multiply–accumulates (MACs), accompanied on-chip by a microcontroller. It was designed for a unified low-power processor architecture that can run operating systems while simultaneously handling complex numeric tasks such as real-time H.264 video encoding.

The Signetics 2650 was an 8-bit microprocessor introduced in July 1975. According to Adam Osborne's book An Introduction to Microprocessors Vol 2: Some Real Products, it was "the most minicomputer-like" of the microprocessors available at the time. A combination of missing features and odd memory access limited its appeal, and the system saw little use in the market.

The Low Pin Count (LPC) bus is a computer bus used on IBM-compatible personal computers to connect low-bandwidth devices to the CPU, such as the BIOS ROM, "legacy" I/O devices, and Trusted Platform Module (TPM). "Legacy" I/O devices usually include serial and parallel ports, PS/2 keyboard, PS/2 mouse, and floppy disk controller.

In computing, channel I/O is a high-performance input/output (I/O) architecture that is implemented in various forms on a number of computer architectures, especially on mainframe computers. In the past, channels were generally implemented with custom devices, variously named channel, I/O processor, I/O controller, I/O synchronizer, or DMA controller.

The Ricoh 5A22 is an 8/16-bit microprocessor produced by Ricoh for the Super Nintendo Entertainment System (SNES) video game console. It is based on the 8/16-bit WDC 65C816, which was developed between 1982 and 1984 for the Apple IIGS personal computer. It has 92 instructions, an 8-bit data bus, a 16-bit accumulator, and a 24-bit address bus. The CPU runs between 1.79 MHz and 3.58 MHz, and uses an extended MOS Technology 6502 instruction set.

In computing, the clock multiplier sets the ratio of an internal CPU clock rate to the externally supplied clock. A CPU with a 10x multiplier will thus see 10 internal cycles for every external clock cycle. For example, a system with an external clock of 100 MHz and a 36x clock multiplier will have an internal CPU clock of 3.6 GHz. The external address and data buses of the CPU also use the external clock as a fundamental timing base; however, they could also employ a (small) multiple of this base frequency to transfer data faster.

The CP1600 is a 16-bit microprocessor created in a partnership between General Instrument and Honeywell in 1975. It was among the first single-chip 16-bit processors; only the Texas Instruments TMS9900 is close in introduction date. The overall design bore a strong resemblance to the PDP-11.

Intel 8237 is a direct memory access (DMA) controller, a part of the MCS 85 microprocessor family. It enables data transfer between memory and the I/O with reduced load on the system's main processor by providing the memory with control signals and memory address information during the DMA transfer.