This is a glossary of terms used in the field of Reconfigurable computing and reconfigurable computing systems, as opposed to the traditional Von Neumann architecture.

- Aggregate On-chip memory

- Refers to total on-chip memory available for multi-FPGA systems.

- Auto-sequencing memory (ASM)

- Anti machine data memory including data counters to be programmed by flowware to generate the data streams at run time.

- Bitstream

- The file that configures the FPGA (has a .bit extension). The bitstream gets loaded into an FPGA when ready for execution. Obtained after place and route, final result of the place and route phase.

- Common Memory

- Should refer to memory on a multi-FPGA board to which all the FPGAs can communicate data to directly and is external to the FPGA.

- Compile/Compilation

- Code segments/pieces that are meant to run on the microprocessor. This could include simulation/emulation runs, which are executing on the processor. Alternatively, this word could be used to encompass the processes of synthesis, and place and route for reconfigurable devices.

- Co-compilation

- Configware/Software-Co-Compilation: Compilation for generating Software Code and Configware Code, including automatic Software/Configware partitioning.

- Configware

- Source programs for Configuration. Being of structural nature, Configware is the counterpart of Software (being of procedural nature).

- Configuration

- Should refer to the bitstream currently loaded on an FPGA. When used loosely, it could also refer to the components/chipset making up a board or reconfigurable machine, which should not be the case.

- Cycle accurate simulation

- Simulation that exactly mimics the clock on the FPGA, records changes in data based on the rising/falling edge of the clock.

- Emulation/Simulation

- Process of mimicking the behavior of an ASIC design on FPGA-based hardware or a processor-based system or (in the case of simulation) a computer.

- Flowware

- In addition to configware, the second programming source needed for data scheduling. Flowware is data-stream-based, in contrast to software which is instruction-stream-based.

- High Performance Computing (HPC)

- Parallel computing based on an array of microprocessors or (Reconfigurable HPC): FPGAs or rDPAs characterized by large run-times and computing resources, parallel implementations of algorithms.

- Hybrid

- In this context the term "hybrid" stands for a symbiosis of procedural (instruction-stream-based) computing and reconfigurable computing (no instruction fetch at run time).

- Hybrid-core

- Hybrid-core computing is the technique of extending a commodity instruction set architecture (e.g. x86) with application-specific instructions to accelerate application performance. It is a form of heterogeneous computing wherein asymmetric computational units coexist with a "commodity" processor.

- Local Memory

- This term should be used purely to describe memory that is external to an FPGA or rDPA, is attached directly to an FPGA, and is not attached to any other FPGA or device on the board or outside of it. It should be called "On-chip memory" when located on board of the same chip with the FPGA or rDPA.

- Morphware

- Another term for Reconfigurable Devices, indicating Reconfigurability in contrast to "hardware".

- On-chip memory

- This term should refer to memory that is available on-chip within a single chip (whether it be BRAM Slices or SRAM slices). The term cache should be reserved purely for memory directly attached to processors on the system/host side.

- Place and Route

- Process of converting a netlist into physically mapped and placed components on the FPGA or rDPA, ending in the creation of a bitstream.

- Reconfigurable Computer

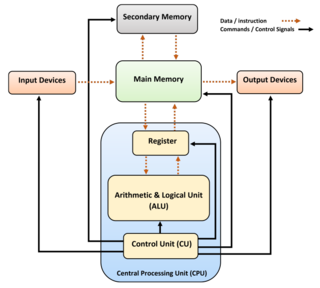

- An Estrin architecture reconfigurable computer typically pairs a conventional microprocessor host computer with a reconfigurable co-processor, such as an FPGA or rDPA board. The co-processor can be reconfigured to perform different computations during execution of a host computer program by loading appropriate bitstreams. Newer FPGA-based architectures eliminate the need for a host processor by providing mechanisms to configure the device on boot from flash and to directly support essential interfaces to memory and network resources via a bus configured in the device fabric. Fairly recent market has developed for low-power reconfigurable system-on-chip (SoC) devices that manufacturers can customize to their product applications, which are typically portable consumer media electronics. The devices typically incorporate one or more von Neumann processors and provide mechanisms to extend the processor(s) instruction set and/or interface the device to other subsystems in the product. While these devices are technically "reconfigurable processors," they are really designed to be configured once during production, or to be reconfigured as part of a field upgrade, but not to be reconfigured on-the-fly.

- Reconfigurable Computing

- A computing paradigm employing reconfigurable devices such as FPGAs or rDPAs to process data. A different bitstream can be loaded during the execution of a program or to run a different program on the fly. Estrin architecture reconfigurable computers include conventional von Neumann processors as main or control processors and typically use one or more reconfigurable devices as co-processors. Newer FPGA-based architectures eliminate the need for a host processor by providing mechanisms to configure the device on boot from flash and to directly support essential interfaces to memory and network resources via a bus configured in the device fabric. Providing a stable and stateful computational platform within a reconfigurable device requires, however, partial reconfigurability - that is, the ability to reconfigure only that portion of the device that implements an application, while leaving unchanged the portion of the device that implements the platform - the memory and network interfaces, the device drivers, and so forth. Current FPGA devices allow partial reconfiguration, but implementing designs that can effectively use this feature is still a tough exercise in system-on-chip design.

- Reconfigurable Device

- FPGAs, rDPAs, and any other device whose functionality can be changed during execution. The reconfigurable device may have a fine-grained architecture like FPGAs, or a coarse-grained architecture like rDPAs. If in a hardware architecture both functionalities of processing elements and interconnections between them can be modified after fabrication time then it is a reconfigurable device or architecture.

- Reconfiguration

- Configuration, programming, re-programming (also see Configware).

- System Memory/Host Memory

- Should refer to memory on the microprocessor motherboard. You could also refer to it as host memory, not cache memory.

- Synthesis

- Process of creating a netlist from a circuit description described using HDLs (Hardware Description Language), HLLs (High Level Language), GUI (Graphical User Interfaces).