This article needs additional citations for verification .(October 2009) (Learn how and when to remove this template message) |

The HITAC S-810 is a vector supercomputer developed, manufactured and marketed by Hitachi. The first models, the S-810/10 and S-810/20, were announced in August 1982, making the S-810 was the second of the first three Japanese supercomputers, following the Fujitsu VP-200, which was announced July 1982, but predating the NEC SX-2, which was announced in April 1983. The S-810 was Hitachi's first supercomputer, although the company had previously built a vector processor, the IAP. The first system shipped was a top-end S-810/20 model, which was delivered to the University of Tokyo's Large Computer Center in October 1983. The S-810 was succeeded as Hitachi's top-end supercomputer by the HITAC S-820 announced in July 1987.

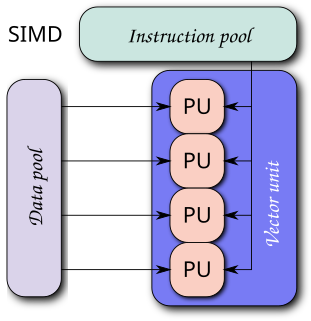

In computing, a vector processor or array processor is a central processing unit (CPU) that implements an instruction set containing instructions that operate on one-dimensional arrays of data called vectors, compared to scalar processors, whose instructions operate on single data items. Vector processors can greatly improve performance on certain workloads, notably numerical simulation and similar tasks. Vector machines appeared in the early 1970s and dominated supercomputer design through the 1970s into the 1990s, notably the various Cray platforms. The rapid fall in the price-to-performance ratio of conventional microprocessor designs led to the vector supercomputer's demise in the later 1990s.

A supercomputer is a computer with a high level of performance compared to a general-purpose computer. The performance of a supercomputer is commonly measured in floating-point operations per second (FLOPS) instead of million instructions per second (MIPS). Since 2017, there are supercomputers which can perform up to nearly a hundred quadrillion FLOPS. Since November 2017, all of the world's fastest 500 supercomputers run Linux-based operating systems. Additional research is being conducted in China, the United States, the European Union, Taiwan and Japan to build even faster, more powerful and more technologically superior exascale supercomputers.

Hitachi, Ltd. is a Japanese multinational conglomerate company headquartered in Chiyoda, Tokyo, Japan. It is the parent company of the Hitachi Group and forms part of the DKB Group of companies. Hitachi is a highly diversified company that operates eleven business segments: Information & Telecommunication Systems, Social Infrastructure, High Functional Materials & Components, Financial Services, Power Systems, Electronic Systems & Equipment, Automotive Systems, Railway & Urban Systems, Digital Media & Consumer Products, Construction Machinery and Other Components & Systems.

There were three models, the low-end S-810/5, the mid-range S-810/10, and the top-end S-810/20. They differ in the number of vector pipelines installed, the number of scalar registers, the number vector registers, and the amount of memory supported. Hitachi claimed that the S-810/5's peak performance was 160 MFLOPS, the S-810/10's was 315 MFLOPS, and the S-810/20's was 630 MFLOPS.

The S-810 implements a Hitachi-designed extension of the IBM System/370 instruction set architecture with 83 vector instructions (80 in the S-810/5 and S-810/10). The vector instructions are register-to-register, meaning that they do not directly reference memory. The scalar processor is a Hitachi HITAC M-280H mainframe with a 28 nanosecond (ns) cycle time (clock rate of approximately 35.71 MHz). In the S-810/20, there are 32 scalar registers, whereas the other models have 16. In all models, the scalar processor has a large 256 kilobyte cache.

International Business Machines Corporation (IBM) is an American multinational information technology company headquartered in Armonk, New York, with operations in over 170 countries. The company began in 1911, founded in Endicott, New York, as the Computing-Tabulating-Recording Company (CTR) and was renamed "International Business Machines" in 1924.

An instruction set architecture (ISA) is an abstract model of a computer. It is also referred to as architecture or computer architecture. A realization of an ISA is called an implementation. An ISA permits multiple implementations that may vary in performance, physical size, and monetary cost ; because the ISA serves as the interface between software and hardware. Software that has been written for an ISA can run on different implementations of the same ISA. This has enabled binary compatibility between different generations of computers to be easily achieved, and the development of computer families. Both of these developments have helped to lower the cost of computers and to increase their applicability. For these reasons, the ISA is one of the most important abstractions in computing today.

Scalar processors represent a class of computer processors. A scalar processor processes only one data item at a time, with typical data items being integers or floating point numbers. A scalar processor is classified as a SISD processor in Flynn's taxonomy.

The vector processor has a 14 ns cycle time (clock rate of approximately 71.43 MHz). The vector registers are 256 elements wide, and each element is 64 bits wide. The S-810/20 has 32 of these registers, whereas the other models have 16. These registers are implemented with 1 kilobit (Kbit) bipolar RAM integrated circuits (ICs) with a 4.5 ns access time. All models have eight 256-bit vector mask registers and 48 vector address registers. All models have three load pipelines and one load/store pipeline for accessing the main memory. The S-810/20 has two lanes, each with two add, one multiply followed by add, and one multiply or divide followed by add floating point pipelines, for a total of twelve. The S-810/10 has one lane with the same configuration as the S-810/20 and therefore a total of six pipelines. CPU logic is implemented with two emitter-coupled logic gate array IC types, a 550-gate part with a 250 picosecond (ps) gate delay and a 1,500-gate part with a 450 ps gate delay.

The kilobit is a multiple of the unit bit for digital information or computer storage. The prefix kilo- (symbol k) is defined in the International System of Units (SI) as a multiplier of 103 (1 thousand), and therefore,

A bipolar junction transistor is a type of transistor that uses both electron and hole charge carriers. In contrast, unipolar transistors, such as field-effect transistors, only use one kind of charge carrier. For their operation, BJTs use two junctions between two semiconductor types, n-type and p-type.

An integrated circuit or monolithic integrated circuit is a set of electronic circuits on one small flat piece of semiconductor material that is normally silicon. The integration of large numbers of tiny transistors into a small chip results in circuits that are orders of magnitude smaller, cheaper, and faster than those constructed of discrete electronic components. The IC's mass production capability, reliability and building-block approach to circuit design has ensured the rapid adoption of standardized ICs in place of designs using discrete transistors. ICs are now used in virtually all electronic equipment and have revolutionized the world of electronics. Computers, mobile phones, and other digital home appliances are now inextricable parts of the structure of modern societies, made possible by the small size and low cost of ICs.

The main memory is implemented with 16 Kbit complementary metal–oxide–semiconductor static random access memory ICs with an access time of 40 ns. The S-810/20 supports 64 to 256 megabyte (MB) of main memory, whereas the other models support 32 to 128 MB.

The megabyte is a multiple of the unit byte for digital information. Its recommended unit symbol is MB. The unit prefix mega is a multiplier of 1000000 (106) in the International System of Units (SI). Therefore, one megabyte is one million bytes of information. This definition has been incorporated into the International System of Quantities.