A complex instruction set computer is a computer in which single instructions can execute several low-level operations or are capable of multi-step operations or addressing modes within single instructions. The term was retroactively coined in contrast to reduced instruction set computer (RISC) and has therefore become something of an umbrella term for everything that is not RISC, from large and complex mainframe computers to simplistic microcontrollers where memory load and store operations are not separated from arithmetic instructions. The only typical differentiating characteristic is that most RISC designs use uniform instruction length for almost all instructions, and employ strictly separate load and store instructions.

A microprocessor is a computer processor that incorporates the functions of a central processing unit on a single integrated circuit (IC) of MOSFET construction. The microprocessor is a multipurpose, clock-driven, register-based, digital integrated circuit that accepts binary data as input, processes it according to instructions stored in its memory, and provides results as output. Microprocessors contain both combinational logic and sequential digital logic. Microprocessors operate on numbers and symbols represented in the binary number system.

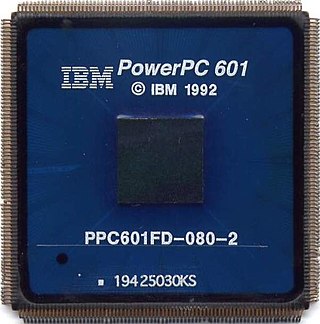

PowerPC is a reduced instruction set computer (RISC) instruction set architecture (ISA) created by the 1991 Apple–IBM–Motorola alliance, known as AIM. PowerPC, as an evolving instruction set, has since 2006 been named Power ISA, while the old name lives on as a trademark for some implementations of Power Architecture–based processors.

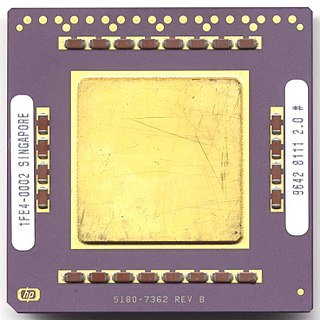

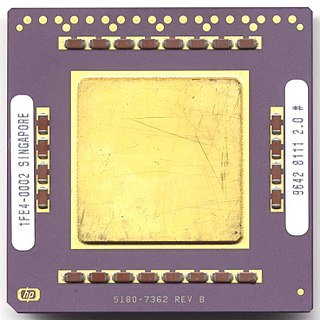

PA-RISC is an instruction set architecture (ISA) developed by Hewlett-Packard. As the name implies, it is a reduced instruction set computer (RISC) architecture, where the PA stands for Precision Architecture. The design is also referred to as HP/PA for Hewlett Packard Precision Architecture.

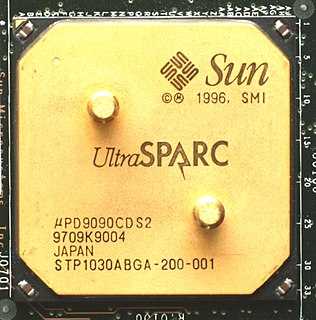

A reduced instruction set computer, or RISC, is a computer with a small, highly optimized set of instructions, rather than the more specialized set often found in other types of architecture, such as in a complex instruction set computer (CISC). The main distinguishing feature of RISC architecture is that the instruction set is optimized with a large number of registers and a highly regular instruction pipeline, allowing a low number of clock cycles per instruction (CPI). Another common RISC feature is the load/store architecture, in which memory is accessed through specific instructions rather than as a part of most instructions in the set.

The 801 was an experimental minicomputer designed by IBM. The resulting architecture was used in various roles in IBM into the 1980s.

The AIM alliance was formed on October 2, 1991 between Apple, IBM, and Motorola to create a new, grandly unified, computing standard based on the POWER instruction set architecture. It was further intended to cope with Microsoft's monopoly and the Wintel duopoly. The alliance yielded the launch of Taligent, Kaleida Labs, the highly successful PowerPC CPU family, the Common Hardware Reference Platform (CHRP) hardware platform standard, and Apple's highly successful Power Macintosh computer line.

The PowerPC 7xx is a family of third generation 32-bit PowerPC microprocessors designed and manufactured by IBM and Motorola. This family is called the PowerPC G3 by its well-known customer Apple Inc., which introduced it on November 10, 1997. The term "PowerPC G3" is often, and incorrectly, imagined to be a microprocessor when in fact a number of microprocessors from different vendors have been used. Such designations were applied to Macintosh computers such as the PowerBook G3, the multicolored iMacs, iBooks and several desktops, including both the Beige and Blue and White Power Macintosh G3s. The low power requirements and small size made the processors ideal for laptops and the name lived out its last days at Apple in the iBook.

The IBM RS64 is a family of microprocessors that were used in the late 1990s in IBM's RS/6000 and AS/400 servers.

David J. Bradley is one of the twelve engineers who worked on the original IBM PC, developing the computer's ROM BIOS code. Bradley is credited for implementing the "Control-Alt-Delete" (Ctrl-Alt-Del) key combination that was used to reboot the computer. Bradley joined IBM in 1975 after earning his doctorate in electrical engineering from Purdue University with a dissertation on computer architectures.

HAL Computer Systems, Inc was a Campbell, California-based computer manufacturer founded in 1990 by Andrew Heller, a principal designer of the original IBM POWER architecture. His idea was to build computers based on a RISC architecture for the commercial market.

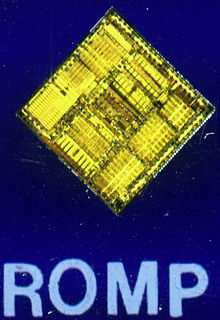

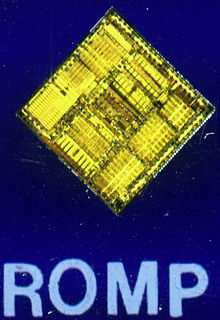

The ROMP is a reduced instruction set computer (RISC) microprocessor designed by IBM in the late 1970s. It is also known as the Research OPD Microprocessor and 032. The ROMP was originally developed for office equipment and small computers, intended as a follow-on to the mid-1970s IBM OPD Mini Processor microprocessor, which was used in the IBM Office System/6 word-processing system. The first examples became available in 1981, and it was first used commercially in the IBM RT PC announced in January 1986. For a time, the RT PC was planned to be a personal computer, with ROMP replacing the Intel 8088 found in the IBM Personal Computer. However, the RT PC was later re-positioned as an engineering and scientific workstation computer. A later CMOS version of the ROMP was first used in the coprocessor board for the IBM 6152 Academic System introduced in 1988, and it later appeared in some models of the RT PC.

Broadway is the codename of the 32-bit Central Processing Unit (CPU) used in Nintendo's Wii video game console. It was designed by IBM, and was initially produced using a 90 nm SOI process and later produced with a 65 nm SOI process.

Keith Diefendorff is a computer architect and veteran in the microprocessor industry.

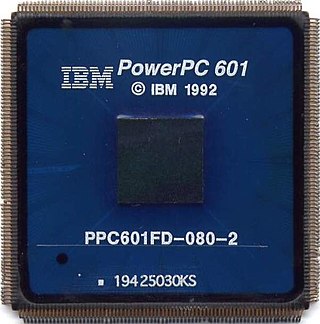

The PowerPC 600 family was the first family of PowerPC processors built. They were designed at the Somerset facility in Austin, Texas, jointly funded and staffed by engineers from IBM and Motorola as a part of the AIM alliance. Somerset was opened in 1992 and its goal was to make the first PowerPC processor and then keep designing general purpose PowerPC processors for personal computers. The first incarnation became the PowerPC 601 in 1993, and the second generation soon followed with the PowerPC 603, PowerPC 604 and the 64-bit PowerPC 620.

The history of general-purpose CPUs is a continuation of the earlier history of computing hardware.

Mark D. Papermaster is an American business executive currently serving as the chief technology officer (CTO) and executive vice president for Technology and Engineering at Advanced Micro Devices (AMD). On January 25, 2019 he was promoted to AMD's Executive Vice President. Papermaster previously worked at IBM from 1982 to 2008, where he was closely involved in the development of PowerPC technology and served two years as vice president of IBM's blade server division. Papermaster's decision to move from IBM to Apple Inc. in 2008 became central to a court case considering the validity and scope of an employee non-compete clause in the technology industry. He became senior vice president of devices hardware engineering at Apple in 2009, with oversight for devices such as the iPhone. In 2010 he left Apple and joined Cisco Systems as a VP of the company's silicon engineering development. Papermaster joined AMD on October 24, 2011, assuming oversight for all of AMD's technology teams and the creation of all of AMD's products, and AMD's corporate technical direction.

The IBM POWER ISA is a reduced instruction set computer (RISC) instruction set architecture (ISA) developed by IBM. The name is an acronym for Performance Optimization With Enhanced RISC.

IBM has a series of high performance microprocessors called POWER followed by a number designating generation, i.e. POWER1, POWER2, POWER3 and so forth up to the latest POWER9. These processors have been used by IBM in their RS/6000, AS/400, pSeries, iSeries, System p, System i and Power Systems line of servers and supercomputers. They have also been used in data storage devices by IBM and by other server manufacturers like Bull and Hitachi.