A control store is the part of a CPU's control unit that stores the CPU's microprogram. It is usually accessed by a microsequencer. A control store implementation whose contents are unalterable is known as a Read Only Memory (ROM) or Read Only Storage (ROS); one whose contents are alterable is known as a Writable Control Store (WCS).

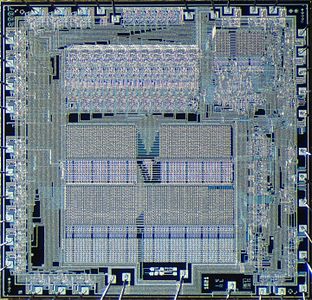

A microprocessor is a computer processor for which the data processing logic and control is included on a single integrated circuit (IC), or a small number of ICs. The microprocessor contains the arithmetic, logic, and control circuitry required to perform the functions of a computer's central processing unit (CPU). The IC is capable of interpreting and executing program instructions and performing arithmetic operations. The microprocessor is a multipurpose, clock-driven, register-based, digital integrated circuit that accepts binary data as input, processes it according to instructions stored in its memory, and provides results as output. Microprocessors contain both combinational logic and sequential digital logic, and operate on numbers and symbols represented in the binary number system.

In processor design, microcode serves as an intermediary layer situated between the central processing unit (CPU) hardware and the programmer-visible instruction set architecture of a computer, also known as its machine code. It consists of a set of hardware-level instructions that implement the higher-level machine code instructions or control internal finite-state machine sequencing in many digital processing components. While microcode is utilized in Intel and AMD general-purpose CPUs in contemporary desktops and laptops, it functions only as a fallback path for scenarios that the faster hardwired control unit is unable to manage.

The PDP–11 is a series of 16-bit minicomputers originally sold by Digital Equipment Corporation (DEC) from 1970 into the late 1990s, one of a set of products in the Programmed Data Processor (PDP) series. In total, around 600,000 PDP-11s of all models were sold, making it one of DEC's most successful product lines. The PDP-11 is considered by some experts to be the most popular minicomputer.

The Intel 4004 is a 4-bit central processing unit (CPU) released by Intel Corporation in 1971. Sold for US$60, it was the first commercially produced microprocessor, and the first in a long line of Intel CPUs.

In electronics and especially synchronous digital circuits, a clock signal is an electronic logic signal which oscillates between a high and a low state at a constant frequency and is used like a metronome to synchronize actions of digital circuits. In a synchronous logic circuit, the most common type of digital circuit, the clock signal is applied to all storage devices, flip-flops and latches, and causes them all to change state simultaneously, preventing race conditions.

Bit slicing is a technique for constructing a processor from modules of processors of smaller bit width, for the purpose of increasing the word length; in theory to make an arbitrary n-bit central processing unit (CPU). Each of these component modules processes one bit field or "slice" of an operand. The grouped processing components would then have the capability to process the chosen full word-length of a given software design.

Pascal MicroEngine is a series of microcomputer products manufactured by Western Digital from 1979 through the mid-1980s, designed specifically to run the UCSD p-System efficiently. Compared to other microcomputers, which use a machine language p-code interpreter, the Pascal MicroEngine has its interpreter implemented in microcode; p-code is its machine language. The most common programming language used on the p-System is Pascal.

The CVAX is a microprocessor chipset developed and fabricated by Digital Equipment Corporation (DEC) that implemented the VAX instruction set architecture (ISA). The chipset consisted of the CVAX 78034 CPU, CFPA floating-point accelerator, CVAX clock chip, and the associated support chips, the CVAX System Support Chip (CSSC), CVAX Memory Controller (CMCTL), and CVAX Q-Bus Interface Chip (CQBIC).

The IMP-16, by National Semiconductor, was the first multi-chip 16-bit microprocessor, released in 1973. It consisted of five PMOS integrated circuits: four identical RALU chips, short for register and ALU, providing the data path, and one CROM, Control and ROM, providing control sequencing and microcode storage. The IMP-16 is a bit-slice processor; each RALU chip provides a 4-bit slice of the register and arithmetic that work in parallel to produce a 16-bit word length.

Joel McCormack is an American computer scientist who designed the NCR Corporation version of the p-code machine, which is a kind of stack machine popular in the 1970s as the preferred way to implement new computing architectures and languages such as Pascal and BCPL. The NCR design shares no common architecture with the Pascal MicroEngine designed by Western Digital but both were meant to execute the UCSD p-System.[1,2]

The V-11, code-named "Scorpio", is a miniprocessor chip set implementation of the VAX instruction set architecture (ISA) developed and fabricated by Digital Equipment Corporation (DEC).

The CP1600 is a 16-bit microprocessor created in a partnership between General Instrument and Honeywell, introduced in February 1975. It is one of the first single-chip 16-bit processors. The overall design bears a strong resemblance to the PDP-11.

The 1801 series CPUs were a family of 16-bit Soviet microprocessors based on the indigenous Elektronika NC microarchitecture cores, but binary compatible with DEC's PDP-11 machines. First released in 1980, various models and variants of the series were among the most popular Soviet microprocessors and dominated embedded systems and military applications of the 1980s. They were also used in widely different areas such as graphing calculators and industrial CNCs, but arguably their most well-known use was in several Soviet general-purpose mini- and microcomputer designs like the SM EVM, DVK, UKNC, and BK families. Due to being the CPU of the popular Elektronika BK home computer, used in its late years as a demo machine, as well as the DVK micros that often offered a first glimpse into the UNIX world, this processor achieved something of a cult status among Soviet and then Russian programmers, and to a lesser extent, international programmers.

In computer architecture, 16-bit integers, memory addresses, or other data units are those that are 16 bits wide. Also, 16-bit central processing unit (CPU) and arithmetic logic unit (ALU) architectures are those that are based on registers, address buses, or data buses of that size. 16-bit microcomputers are microcomputers that use 16-bit microprocessors.

Intel microcode is microcode that runs inside x86 processors made by Intel. Since the P6 microarchitecture introduced in the mid-1990s, the microcode programs can be patched by the operating system or BIOS firmware to work around bugs found in the CPU after release. Intel had originally designed microcode updates for processor debugging under its design for testing (DFT) initiative.

The Texas Instruments SBP0400, also known as SBC 0400 and X0400, is a microprogrammable 4-bit slice processor that was introduced in 1976. It was one of the first LSI processors and was the first device in the USA based on I²L technology. It was used for research and teaching purposes in the aerospace industry (NASA) and in the learning computer LCM-1001. This microprocessor learning computer was probably the company's first.

The Mostek MK5065 was an 8-bit microprocessor introduced by Mostek in early 1974. The design was originally developed by Motorola for use in an Olivetti electronic calculator, and was licensed to Mostek for use in non-calculator roles. It featured three sets of processor registers, allowing it to switch to an interrupt handler in a single cycle, and a wait-for-data mode that aided direct memory access.

The NCR/32 VLSI Processor family was a 32-bit microprocessor architecture and chipset developed by NCR Corporation in the early 1980s. Generally used in minicomputer systems, it was noteworthy for being externally microprogrammable.