Related Research Articles

The VHSIC Hardware Description Language (VHDL) is a hardware description language (HDL) that can model the behavior and structure of digital systems at multiple levels of abstraction, ranging from the system level down to that of logic gates, for design entry, documentation, and verification purposes. Since 1987, VHDL has been standardized by the Institute of Electrical and Electronics Engineers (IEEE) as IEEE Std 1076; the latest version of which is IEEE Std 1076-2019. To model analog and mixed-signal systems, an IEEE-standardized HDL based on VHDL called VHDL-AMS has been developed.

Verilog, standardized as IEEE 1364, is a hardware description language (HDL) used to model electronic systems. It is most commonly used in the design and verification of digital circuits at the register-transfer level of abstraction. It is also used in the verification of analog circuits and mixed-signal circuits, as well as in the design of genetic circuits. In 2009, the Verilog standard was merged into the SystemVerilog standard, creating IEEE Standard 1800-2009. Since then, Verilog is officially part of the SystemVerilog language. The current version is IEEE standard 1800-2017.

In computer engineering, a hardware description language (HDL) is a specialized computer language used to describe the structure and behavior of electronic circuits, and most commonly, digital logic circuits.

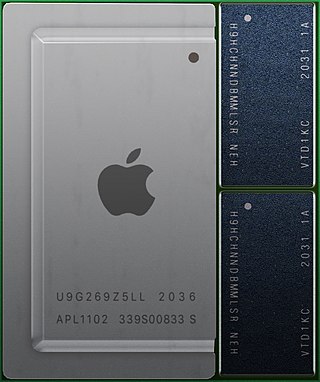

A system on a chip or system-on-chip is an integrated circuit that integrates most or all components of a computer or other electronic system. These components almost always include on-chip central processing unit (CPU), memory interfaces, input/output devices and interfaces, and secondary storage interfaces, often alongside other components such as radio modems and a graphics processing unit (GPU) – all on a single substrate or microchip. SoCs may contain digital and also analog, mixed-signal and often radio frequency signal processing functions.

Mentor Graphics Corporation was a US-based electronic design automation (EDA) multinational corporation for electrical engineering and electronics, headquartered in Wilsonville, Oregon. Founded in 1981, the company distributed products that assist in electronic design automation, simulation tools for analog mixed-signal design, VPN solutions, and fluid dynamics and heat transfer tools. The company leveraged Apollo Computer workstations to differentiate itself within the computer-aided engineering (CAE) market with its software and hardware.

SystemC is a set of C++ classes and macros which provide an event-driven simulation interface. These facilities enable a designer to simulate concurrent processes, each described using plain C++ syntax. SystemC processes can communicate in a simulated real-time environment, using signals of all the datatypes offered by C++, some additional ones offered by the SystemC library, as well as user defined. In certain respects, SystemC deliberately mimics the hardware description languages VHDL and Verilog, but is more aptly described as a system-level modeling language.

Formal equivalence checking process is a part of electronic design automation (EDA), commonly used during the development of digital integrated circuits, to formally prove that two representations of a circuit design exhibit exactly the same behavior.

In computer engineering, logic synthesis is a process by which an abstract specification of desired circuit behavior, typically at register transfer level (RTL), is turned into a design implementation in terms of logic gates, typically by a computer program called a synthesis tool. Common examples of this process include synthesis of designs specified in hardware description languages, including VHDL and Verilog. Some synthesis tools generate bitstreams for programmable logic devices such as PALs or FPGAs, while others target the creation of ASICs. Logic synthesis is one step in circuit design in the electronic design automation, the others are place and route and verification and validation.

In semiconductor design, standard-cell methodology is a method of designing application-specific integrated circuits (ASICs) with mostly digital-logic features. Standard-cell methodology is an example of design abstraction, whereby a low-level very-large-scale integration (VLSI) layout is encapsulated into an abstract logic representation.

SystemVerilog, standardized as IEEE 1800, is a hardware description and hardware verification language used to model, design, simulate, test and implement electronic systems. SystemVerilog is based on Verilog and some extensions, and since 2008, Verilog is now part of the same IEEE standard. It is commonly used in the semiconductor and electronic design industry as an evolution of Verilog.

Electronic system level (ESL) design and verification is an electronic design methodology, focused on higher abstraction level concerns. The term Electronic System Level or ESL Design was first defined by Gartner Dataquest, an EDA-industry-analysis firm, on February 1, 2001. It is defined in ESL Design and Verification as: "the utilization of appropriate abstractions in order to increase comprehension about a system, and to enhance the probability of a successful implementation of functionality in a cost-effective manner."

Transaction-level modeling (TLM) is an approach to modelling complex digital systems by using electronic design automation software. TLM language (TLML) is a hardware description language, usually, written in C++ and based on SystemC library. TLMLs are used for modelling where details of communication among modules are separated from the details of the implementation of functional units or of the communication architecture. It's used for modelling of systems that involve complex data communication mechanisms.

C to HDL tools convert C language or C-like computer code into a hardware description language (HDL) such as VHDL or Verilog. The converted code can then be synthesized and translated into a hardware device such as a field-programmable gate array. Compared to software, equivalent designs in hardware consume less power and execute faster with lower latency, more parallelism and higher throughput. However, system design and functional verification in a hardware description language can be tedious and time-consuming, so systems engineers often write critical modules in HDL and other modules in a high-level language and synthesize these into HDL through C to HDL or high-level synthesis tools.

Semulation is a computer science-related portmanteau of simulation and emulation, signifying the process of controlling an emulation through a simulator.

A Bus Functional Model or BFM is a non-synthesizable software model of an integrated circuit component having one or more external buses. The emphasis of the model is on simulating system bus transactions prior to building and testing the actual hardware. BFMs are usually defined as tasks in Hardware description languages (HDLs), which apply stimuli to the design under verification via complex waveforms and protocols. A BFM is typically implemented using hardware description languages such as Verilog, VHDL, SystemC, or SystemVerilog.

ModelSim is a multi-language environment by Siemens for simulation of hardware description languages such as VHDL, Verilog and SystemC, and includes a built-in C debugger. ModelSim can be used independently, or in conjunction with Intel Quartus Prime, PSIM, Xilinx ISE or Xilinx Vivado. Simulation is performed using the graphical user interface (GUI), or automatically using scripts.

High-level synthesis (HLS), sometimes referred to as C synthesis, electronic system-level (ESL) synthesis, algorithmic synthesis, or behavioral synthesis, is an automated design process that takes an abstract behavioral specification of a digital system and finds a register-transfer level structure that realizes the given behavior.

Forte Design Systems, Inc. was a San Jose, CA, based provider of high-level synthesis (HLS) software products, also known as electronic system-level (ESL) synthesis. Forte's main product was Cynthesizer. On February 14, 2014, Forte was acquired by Cadence Design Systems.

High-level verification (HLV), or electronic system-level (ESL) verification, is the task to verify ESL designs at high abstraction level, i.e., it is the task to verify a model that represents hardware above register-transfer level (RTL) abstract level. For high-level synthesis, HLV is to HLS as functional verification is to logic synthesis.

EVE/ZeBu is a provider of hardware-assisted verification tools for functional verification of Application-specific integrated circuits (ASICs) and system on chip (SOC) designs and for validation of embedded software ahead of implementation in silicon. EVE's hardware acceleration and hardware emulation products work in conjunction with Verilog, SystemVerilog, and VHDL-based simulators from Synopsys, Cadence Design Systems and Mentor Graphics. EVE's flagship product is ZeBu.

References

- ↑ Chip Design Bridging ESL and High-Level Synthesis

- ↑ University of Oulu Rapid Scheduling of Efficient VLSI Architectures for Next-Generation HSDPA Wireless System Using C Synthesis

- ↑ EETimes: High-level synthesis rollouts enable ESL

- ↑ SOCCentral Mentor Graphics Extends Catapult C Synthesis Product Archived 2006-02-05 at the Wayback Machine

- ↑ SOCCentral Mentor Introduces High-Level Synthesis to Create High-Performance Subsystems from Pure ANSI C++ Archived 2012-09-13 at archive.today .

- ↑ EETimes Mentor TLM 2.0 design flow

- ↑ SCDsource Mentor Catapult C synthesizes control and power management Archived 2011-10-09 at the Wayback Machine

- ↑ Chip Design Bridging ESL and High-Level Synthesis

- ↑ EETimes Mentor’s TLM Synthesis links virtual prototyping and hardware implementation

- ↑ EETimes Calypto acquires Mentor's Catapult C

- ↑ PR Newswire Mentor Graphics Acquires Calypto Design Systems

- ↑ University of Oulu Rapid Scheduling of Efficient VLSI Architectures for Next-Generation HSDPA Wireless System Using C Synthesis

- ↑ SCDsource Mentor Catapult C synthesizes control and power management Archived 2011-10-09 at the Wayback Machine

- ↑ ICASSP Architectural Design and Implementation of the Increasing Radius – List Sphere Detector Algorithm

- ↑ Deepchip C/C++ chip design using high-level synthesis

- ↑ EETimes Mentor’s TLM Synthesis links virtual prototyping and hardware implementation