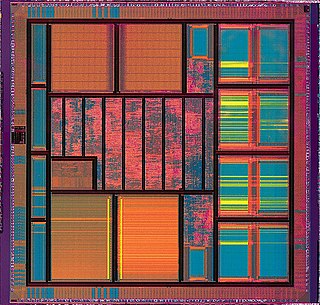

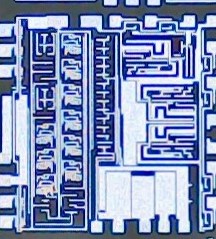

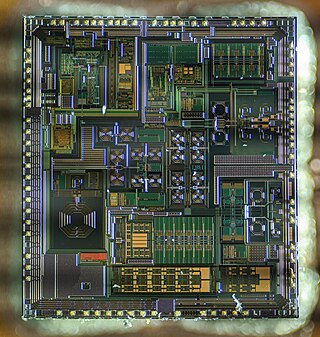

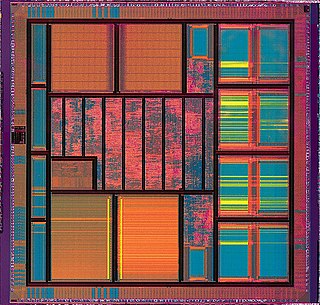

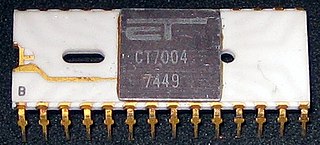

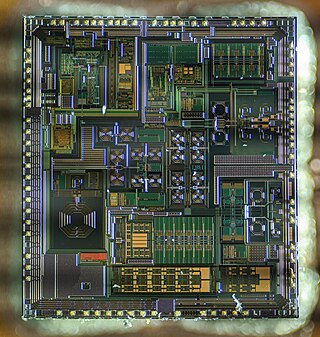

An integrated circuit (IC), also known as a microchip or simply chip, is a small electronic device made up of multiple interconnected electronic components such as transistors, resistors, and capacitors. These components are etched onto a small piece of semiconductor material, usually silicon. Integrated circuits are used in a wide range of electronic devices, including computers, smartphones, and televisions, to perform various functions such as processing and storing information. They have greatly impacted the field of electronics by enabling device miniaturization and enhanced functionality.

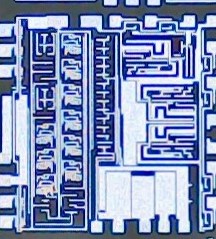

Very-large-scale integration (VLSI) is the process of creating an integrated circuit (IC) by combining millions or billions of MOS transistors onto a single chip. VLSI began in the 1970s when MOS integrated circuit chips were developed and then widely adopted, enabling complex semiconductor and telecommunications technologies. The microprocessor and memory chips are VLSI devices.

In electronics, the metal–oxide–semiconductor field-effect transistor is a type of field-effect transistor (FET), most commonly fabricated by the controlled oxidation of silicon. It has an insulated gate, the voltage of which determines the conductivity of the device. This ability to change conductivity with the amount of applied voltage can be used for amplifying or switching electronic signals. The term metal–insulator–semiconductor field-effect transistor (MISFET) is almost synonymous with MOSFET. Another near-synonym is insulated-gate field-effect transistor (IGFET).

Complementary metal–oxide–semiconductor is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) fabrication process that uses complementary and symmetrical pairs of p-type and n-type MOSFETs for logic functions. CMOS technology is used for constructing integrated circuit (IC) chips, including microprocessors, microcontrollers, memory chips, and other digital logic circuits. CMOS technology is also used for analog circuits such as image sensors, data converters, RF circuits, and highly integrated transceivers for many types of communication.

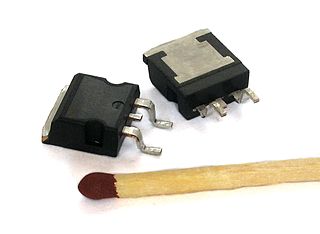

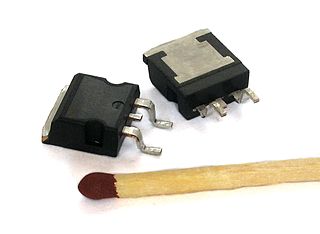

An insulated-gate bipolar transistor (IGBT) is a three-terminal power semiconductor device primarily forming an electronic switch. It was developed to combine high efficiency with fast switching. It consists of four alternating layers (NPNP) that are controlled by a metal–oxide–semiconductor (MOS) gate structure.

Bipolar CMOS (BiCMOS) is a semiconductor technology that integrates two semiconductor technologies, those of the bipolar junction transistor and the CMOS logic gate, into a single integrated circuit. In more recent times the bipolar processes have been extended to include high mobility devices using silicon–germanium junctions.

In computer engineering, a logic family is one of two related concepts:

A mixed-signal integrated circuit is any integrated circuit that has both analog circuits and digital circuits on a single semiconductor die. Their usage has grown dramatically with the increased use of cell phones, telecommunications, portable electronics, and automobiles with electronics and digital sensors.

In integrated circuits, depletion-load NMOS is a form of digital logic family that uses only a single power supply voltage, unlike earlier NMOS logic families that needed more than one different power supply voltage. Although manufacturing these integrated circuits required additional processing steps, improved switching speed and the elimination of the extra power supply made this logic family the preferred choice for many microprocessors and other logic elements.

Transistors are simple devices with complicated behavior. In order to ensure the reliable operation of circuits employing transistors, it is necessary to scientifically model the physical phenomena observed in their operation using transistor models. There exists a variety of different models that range in complexity and in purpose. Transistor models divide into two major groups: models for device design and models for circuit design.

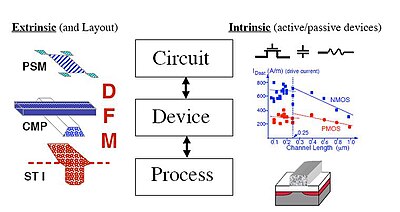

Technology computer-aided design is a branch of electronic design automation (EDA) that models semiconductor fabrication and semiconductor device operation. The modeling of the fabrication is termed process TCAD, while the modeling of the device operation is termed device TCAD. Included are the modelling of process steps, and modelling of the behavior of the electrical devices based on fundamental physics, such as the doping profiles of the devices. TCAD may also include the creation of "compact models", which try to capture the electrical behavior of such devices but do not generally derive them from the underlying physics. SPICE simulator itself is usually considered as part of EDA rather than TCAD.

Semiconductor process simulation is the modeling of the fabrication of semiconductor devices such as transistors. It is a branch of electronic design automation, and part of a sub-field known as technology CAD (TCAD).

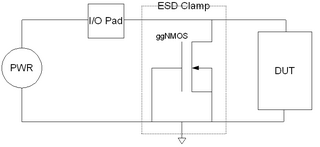

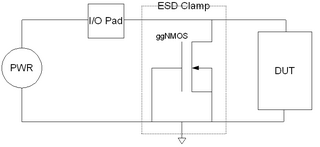

Grounded-gate NMOS, commonly known as ggNMOS, is an electrostatic discharge (ESD) protection device used within CMOS integrated circuits (ICs). Such devices are used to protect the inputs and outputs of an IC, which can be accessed off-chip and are therefore subject to ESD when touched. An ESD event can deliver a large amount of energy to the chip, potentially destroying input/output circuitry; a ggNMOS device or other ESD protective devices provide a safe path for current to flow, instead of through more sensitive circuitry. ESD protection by means of such devices or other techniques is important to product reliability: 35% of all IC failures in the field are associated with ESD damage.

PMOS or pMOS logic is a family of digital circuits based on p-channel, enhancement mode metal–oxide–semiconductor field-effect transistors (MOSFETs). In the late 1960s and early 1970s, PMOS logic was the dominant semiconductor technology for large-scale integrated circuits before being superseded by NMOS and CMOS devices.

Chih-Tang "Tom" Sah is a Chinese-American electronics engineer and condensed matter physicist. He is best known for inventing CMOS logic with Frank Wanlass at Fairchild Semiconductor in 1963. CMOS is used in nearly all modern very large-scale integration (VLSI) semiconductor devices.

Process variation is the naturally occurring variation in the attributes of transistors when integrated circuits are fabricated. The amount of process variation becomes particularly pronounced at smaller process nodes (<65 nm) as the variation becomes a larger percentage of the full length or width of the device and as feature sizes approach the fundamental dimensions such as the size of atoms and the wavelength of usable light for patterning lithography masks.

Robert W. Dutton is an American electrical engineer. At Stanford University, he is the Robert and Barbara Kleist Professor of Electrical Engineering, Emeritus. Dutton also served as the undergraduate advisor for Stanford University Department of Electrical Engineering, succeeded by John M. Pauly.

RF CMOS is a metal–oxide–semiconductor (MOS) integrated circuit (IC) technology that integrates radio-frequency (RF), analog and digital electronics on a mixed-signal CMOS RF circuit chip. It is widely used in modern wireless telecommunications, such as cellular networks, Bluetooth, Wi-Fi, GPS receivers, broadcasting, vehicular communication systems, and the radio transceivers in all modern mobile phones and wireless networking devices. RF CMOS technology was pioneered by Pakistani engineer Asad Ali Abidi at UCLA during the late 1980s to early 1990s, and helped bring about the wireless revolution with the introduction of digital signal processing in wireless communications. The development and design of RF CMOS devices was enabled by van der Ziel's FET RF noise model, which was published in the early 1960s and remained largely forgotten until the 1990s.

Yuan Taur is a Chinese American electrical engineer and an academic. He is a Distinguished Professor of Electrical and Computer Engineering (ECE) at the University of California, San Diego.