Computer models

nCUBE 10

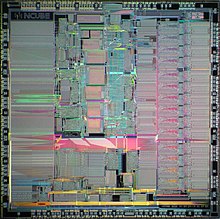

One of the first nCUBE machines to be released was the nCUBE 10 of late 1985. It was originally called NCUBE/ten but the name morphed over time. These were based on a set of custom chips, where each compute node had a processor chip with 32-bit ALU, a 64-bit IEEE 754 FPU, special communication instructions, and 128 KB of RAM. A node delivered 2 MIPS, 500 kiloFLOPS (32-bit single precision), or 300 kiloFLOPS (64-bit double precision). There were 64 nodes per board. The host board, based on an Intel 80286, ran Axis, a custom Unix-like operating system, and each compute node ran a 4 KB kernel, Vertex. [11]

nCUBE 10 referred to the machine's ability to build an order-ten hypercube, supporting 1,024 CPUs in a single machine. Some of the modules would be used strictly for input/output, which included the nChannel storage control card, frame buffers, and the InterSystem card that allowed nCUBEs to be attached to each other. At least one host board needed to be installed, acting as the terminal driver. It could also partition the machine into "sub-cubes" and allocate them separately to different users.

nCUBE 2

For the second series the naming was changed, and they created the single-chip nCUBE 2 processor. This was otherwise similar to the nCUBE 10's CPU, but ran faster, at 25 MHz to provide about 7 MIPS and 3.5 megaFLOPS. This was later improved to 30 MHz in the 2S model. RAM was increased as well, with 4 to 16 MB of RAM on a "single wide" 1 inch x 3.5 inch module, with additional form factors of "double wide" (double modules), and quadruple that in a double wide, double side module. The I/O cards generally had less RAM, with different backend interfaces to support SCSI, HIPPI and other protocols.

Each nCUBE 2 CPU also included 13 I/O channels running at 20 Mbit/s. One of these was dedicated to I/O duties, while the other twelve were used as the interconnect system between CPUs. Each channel used wormhole routing to forward messages. The machines themselves were wired up as order-twelve hypercubes, allowing for up to 4,096 CPUs in a single machine.

Each module ran a 200 KB microkernel called nCX, but the system now used a Sun Microsystems workstation as the front end and no longer needed the Host Controller. nCX included a parallel filesystem that could do 96-way striping for high performance. C and C++ languages are available, as is NQS, Linda, and Parasoft's Express. These were supported by an in-house compiler team.

The largest nCUBE 2 system installed was at Sandia National Laboratories, a 1,024-CPU system that reached 1.91 gigaFLOPS in testing. In addition the nCX operating system, it also ran the SUNMOS lightweight kernel for research purposes. [12] Researchers Robert Benner, John Gustafson and Gary Montry of the Parallel Processing Division of Sandia National Laboratory first won the Karp Prize of $100 and then won the first Gordon Bell Prize in 1987 using the nCUBE 10. [13]

nCUBE-3

The nCUBE-3 CPU used a 64-bit arithmetic logic unit (ALU). Its improvements included a process-shrink to 0.5u, allowing the speed to be increased to 50 MHz (with plans for 66 and 100 MHz). The CPU was also superscalar and included 16 KB instruction and data caches, and a memory management unit for virtual memory support.

Additional I/O links were added, with 2 dedicated to I/O and 16 for interconnects, allowing for up to 65,536 CPUs in the hypercube. The channels operated at 100 Mbit/s, due to use of 2-bit parallel lines, instead of the serial lines used previously. The nCUBE-3 also added fault-tolerant adaptive routing support, in addition to fixed routing, although in retrospect it's not entirely clear why.

A fully loaded nCUBE-3 machine can use up to 65,536 processors, for 3 million MIPS and 6.5 teraFLOPS; the maximum memory would be 65 TB, with a network I/O capability of 24 TB/second. [14] Thus, the processor is biased in terms of I/O, which is usually the limitation. The nChannel board provides 16 I/O channels, where each channel can support transfers at 20 MB/s.

A microkernel was developed for the nCUBE-3 machine, but it was never completed, having been abandoned in favor of Plan 9's Transit operating system.

nCUBE-4

The nCUBE-4 marked the transition to commodity processors, with each node containing an Intel IA32 server-class CPU. The n4 also brought exclusive focus on video streaming rather than scientific applications. Each hub contained one hypercube node, one CPU, a pair of PCI buses, and up to 12 SCSI drives. The n4 was followed by the n4x, the n4x r2, and the n4x r3. These last two were based on the Serverworks chipset rather than the Intel ones. The nCUBE-5 was very similar to the n4 family but incorporated two hypercube nodes in each hub and only supported video streaming over Gigabit Ethernet.

In 1999, nCUBE announced the MediaCUBE 4, which supported 80 simultaneous 3 Mbit/s streams to 44,000 simultaneous VOD streams, in concurrent MPEG-2, MPEG-1 and mid bit-rate encoding protocols. [15]