A printed circuit board (PCB), also called printed wiring board (PWB), is a medium used to connect or "wire" components to one another in a circuit. It takes the form of a laminated sandwich structure of conductive and insulating layers: each of the conductive layers is designed with a pattern of traces, planes and other features etched from one or more sheet layers of copper laminated onto or between sheet layers of a non-conductive substrate. Electrical components may be fixed to conductive pads on the outer layers, generally by means of soldering, which both electrically connects and mechanically fastens the components to the board. Another manufacturing process adds vias, drilled holes that allow electrical interconnections between conductive layers.

A ball grid array (BGA) is a type of surface-mount packaging used for integrated circuits. BGA packages are used to permanently mount devices such as microprocessors. A BGA can provide more interconnection pins than can be put on a dual in-line or flat package. The whole bottom surface of the device can be used, instead of just the perimeter. The traces connecting the package's leads to the wires or balls which connect the die to package are also on average shorter than with a perimeter-only type, leading to better performance at high speeds.

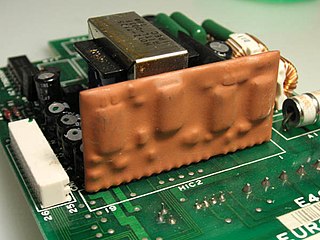

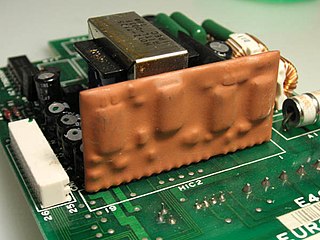

A heat sink is a passive heat exchanger that transfers the heat generated by an electronic or a mechanical device to a fluid medium, often air or a liquid coolant, where it is dissipated away from the device, thereby allowing regulation of the device's temperature. In computers, heat sinks are used to cool CPUs, GPUs, and some chipsets and RAM modules. Heat sinks are used with other high-power semiconductor devices such as power transistors and optoelectronics such as lasers and light-emitting diodes (LEDs), where the heat dissipation ability of the component itself is insufficient to moderate its temperature.

Flip chip, also known as controlled collapse chip connection or its abbreviation, C4, is a method for interconnecting dies such as semiconductor devices, IC chips, integrated passive devices and microelectromechanical systems (MEMS), to external circuitry with solder bumps that have been deposited onto the chip pads. The technique was developed by General Electric's Light Military Electronics Department, Utica, New York. The solder bumps are deposited on the chip pads on the top side of the wafer during the final wafer processing step. In order to mount the chip to external circuitry, it is flipped over so that its top side faces down, and aligned so that its pads align with matching pads on the external circuit, and then the solder is reflowed to complete the interconnect. This is in contrast to wire bonding, in which the chip is mounted upright and fine wires are welded onto the chip pads and lead frame contacts to interconnect the chip pads to external circuitry.

Integrated circuit packaging is the final stage of semiconductor device fabrication, in which the die is encapsulated in a supporting case that prevents physical damage and corrosion. The case, known as a "package", supports the electrical contacts which connect the device to a circuit board.

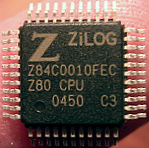

A quad flat package (QFP) is a surface-mounted integrated circuit package with "gull wing" leads extending from each of the four sides. Socketing such packages is rare and through-hole mounting is not possible. Versions ranging from 32 to 304 pins with a pitch ranging from 0.4 to 1.0 mm are common. Other special variants include low-profile QFP (LQFP) and thin QFP (TQFP).

A hybrid integrated circuit (HIC), hybrid microcircuit, hybrid circuit or simply hybrid is a miniaturized electronic circuit constructed of individual devices, such as semiconductor devices and passive components, bonded to a substrate or printed circuit board (PCB). A PCB having components on a Printed wiring board (PWB) is not considered a true hybrid circuit according to the definition of MIL-PRF-38534.

A via is an electrical connection between two or more metal layers of a printed circuit boards (PCB) or integrated circuit. Essentially a via is a small drilled hole that goes through two or more adjacent layers; the hole is plated with metal that forms an electrical connection through the insulating layers.

A power module or power electronic module provides the physical containment for several power components, usually power semiconductor devices. These power semiconductors are typically soldered or sintered on a power electronic substrate that carries the power semiconductors, provides electrical and thermal contact and electrical insulation where needed. Compared to discrete power semiconductors in plastic housings as TO-247 or TO-220, power packages provide a higher power density and are in many cases more reliable.

Flat no-leads packages such as quad-flat no-leads (QFN) and dual-flat no-leads (DFN) physically and electrically connect integrated circuits to printed circuit boards. Flat no-leads, also known as micro leadframe (MLF) and SON, is a surface-mount technology, one of several package technologies that connect ICs to the surfaces of PCBs without through-holes. Flat no-lead is a near chip scale plastic encapsulated package made with a planar copper lead frame substrate. Perimeter lands on the package bottom provide electrical connections to the PCB. Flat no-lead packages usually, but not always, include an exposed thermally conductive pad to improve heat transfer out of the IC. Heat transfer can be further facilitated by metal vias in the thermal pad. The QFN package is similar to the quad-flat package (QFP), and a ball grid array (BGA).

A ceramic capacitor is a fixed-value capacitor where the ceramic material acts as the dielectric. It is constructed of two or more alternating layers of ceramic and a metal layer acting as the electrodes. The composition of the ceramic material defines the electrical behavior and therefore applications. Ceramic capacitors are divided into two application classes:

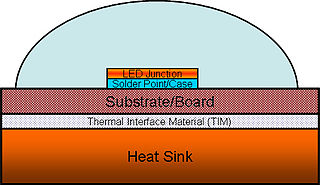

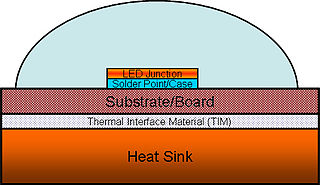

High power light-emitting diodes (LEDs) can use 350 milliwatts or more in a single LED. Most of the electricity in an LED becomes heat rather than light. If this heat is not removed, the LEDs run at high temperatures, which not only lowers their efficiency, but also makes the LED less reliable. Thus, thermal management of high power LEDs is a crucial area of research and development. It is necessary to limit both the junction and the phosphor particles temperatures to a value that will guarantee the desired LED lifetime.

The thermal copper pillar bump, also known as the "thermal bump", is a thermoelectric device made from thin-film thermoelectric material embedded in flip chip interconnects for use in electronics and optoelectronic packaging, including: flip chip packaging of CPU and GPU integrated circuits (chips), laser diodes, and semiconductor optical amplifiers (SOA). Unlike conventional solder bumps that provide an electrical path and a mechanical connection to the package, thermal bumps act as solid-state heat pumps and add thermal management functionality locally on the surface of a chip or to another electrical component. The diameter of a thermal bump is 238 μm and 60 μm high.

Thick-film technology is used to produce electronic devices/modules such as surface mount devices modules, hybrid integrated circuits, heating elements, integrated passive devices and sensors. The main manufacturing technique is screen printing (stenciling), which in addition to use in manufacturing electronic devices can also be used for various graphic reproduction targets. It became one of the key manufacturing/miniaturisation techniques of electronic devices/modules during 1950s. Typical film thickness – manufactured with thick film manufacturing processes for electronic devices – is 0.0001 to 0.1 mm.

Soldering is a process of joining two metal surfaces together using a filler metal called solder. The soldering process involves heating the surfaces to be joined and melting the solder, which is then allowed to cool and solidify, creating a strong and durable joint.

Electronic components have a wide range of failure modes. These can be classified in various ways, such as by time or cause. Failures can be caused by excess temperature, excess current or voltage, ionizing radiation, mechanical shock, stress or impact, and many other causes. In semiconductor devices, problems in the device package may cause failures due to contamination, mechanical stress of the device, or open or short circuits.

Glass frit bonding, also referred to as glass soldering or seal glass bonding, describes a wafer bonding technique with an intermediate glass layer. It is a widely used encapsulation technology for surface micro-machined structures, e.g., accelerometers or gyroscopes. This technique utilizes low melting-point glass and therefore provides various advantages including that viscosity of glass decreases with an increase of temperature. The viscous flow of glass has effects to compensate and planarize surface irregularities, convenient for bonding wafers with a high roughness due to plasma etching or deposition. A low viscosity promotes hermetically sealed encapsulation of structures based on a better adaption of the structured shapes. Further, the coefficient of thermal expansion (CTE) of the glass material is adapted to silicon. This results in low stress in the bonded wafer pair. The glass has to flow and wet the soldered surfaces well below the temperature where deformation or degradation of either of the joined materials or nearby structures occurs. The usual temperature of achieving flowing and wetting is between 450 and 550 °C.

Photoimageable thick-film technology is a combination of conventional thick film technology with elements of thin film technology, and it provides a low cost solution to producing high quality microwave circuits. The ability to directly photoimage the printed layers means that the technology can provide the high line and gap resolution required by high frequency planar components. It provides a feasible fabrication process to produce circuits operating at microwave and millimetre-wave frequencies. Circuits made using this technology meet the modern requirements for high density packaging, whilst yielding the high quality components required for very high frequency applications, including wireless communication, radar and measurement systems.

Co-fired ceramic devices are monolithic, ceramic microelectronic devices where the entire ceramic support structure and any conductive, resistive, and dielectric materials are fired in a kiln at the same time. Typical devices include capacitors, inductors, resistors, transformers, and hybrid circuits. The technology is also used for robust assembly and packaging of electronic components multi-layer packaging in the electronics industry, such as military electronics, MEMS, microprocessor and RF applications.