The Efficeon processor is Transmeta's second-generation 256-bit VLIW design released in 2004 which employs a software engine Code Morphing Software (CMS) to convert code written for x86 processors to the native instruction set of the chip. Like its predecessor, the Transmeta Crusoe, Efficeon stresses computational efficiency, low power consumption, and a low thermal footprint.

Sempron has been the marketing name used by AMD for several different budget desktop CPUs, using several different technologies and CPU socket formats. The Sempron replaced the AMD Duron processor and competed against Intel's Celeron series of processors. AMD coined the name from the Latin semper, which means "always", to suggest the Sempron is suitable for "daily use, practical, and part of everyday life". The last Semprons were launched in April 2014. The brand was retired with the launch of the AMD A-Series APUs.

The PowerPC 400 family is a line of 32-bit embedded RISC processor cores based on the PowerPC or Power ISA instruction set architectures. The cores are designed to fit inside specialized applications ranging from system-on-a-chip (SoC) microcontrollers, network appliances, application-specific integrated circuits (ASICs) and field-programmable gate arrays (FPGAs) to set-top boxes, storage devices and supercomputers.

The AMD Family 10h, or K10, is a microprocessor microarchitecture by AMD based on the K8 microarchitecture. The first third-generation Opteron products for servers were launched on September 10, 2007, with the Phenom processors for desktops following and launching on November 11, 2007 as the immediate successors to the K8 series of processors.

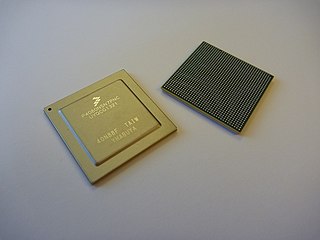

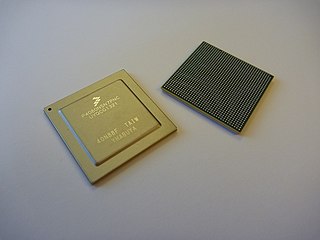

The PowerPC e600 is a family of 32-bit PowerPC microprocessor cores developed by Freescale for primary use in high performance system-on-a-chip (SoC) designs with speed ranging over 2 GHz, thus making them ideal for high performance routing and telecommunications applications. The e600 is the continuation of the PowerPC 74xx design.

Phenom is the 64-bit AMD desktop processor line based on the K10 microarchitecture, in what AMD calls family 10h processors, sometimes incorrectly called "K10h". Triple-core versions belong to the Phenom 8000 series and quad cores to the AMD Phenom X4 9000 series. The first processor in the family was released in 2007.

AMD Turion is the brand name AMD applies to its x86-64 low-power consumption mobile processors codenamed K8L. The Turion 64 and Turion 64 X2/Ultra processors compete with Intel's mobile processors, initially the Pentium M and the Intel Core and Intel Core 2 processors.

TILE64 is a VLIW ISA multicore processor manufactured by Tilera. It consists of a mesh network of 64 "tiles", where each tile houses a general purpose processor, cache, and a non-blocking router, which the tile uses to communicate with the other tiles on the processor.

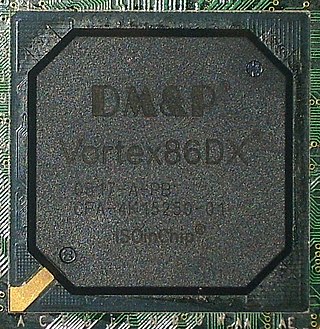

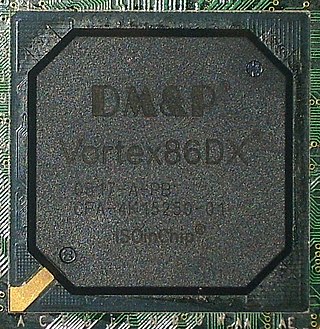

The Vortex86 is a computing system-on-a-chip (SoC) based on a core compatible with the x86 microprocessor family. It is produced by DM&P Electronics, but originated with Rise Technology.

QorIQ is a brand of ARM-based and Power ISA–based communications microprocessors from NXP Semiconductors. It is the evolutionary step from the PowerQUICC platform, and initial products were built around one or more e500mc cores and came in five different product platforms, P1, P2, P3, P4, and P5, segmented by performance and functionality. The platform keeps software compatibility with older PowerPC products such as the PowerQUICC platform. In 2012 Freescale announced ARM-based QorIQ offerings beginning in 2013.

Phenom II is a family of AMD's multi-core 45 nm processors using the AMD K10 microarchitecture, succeeding the original Phenom. Advanced Micro Devices released the Socket AM2+ version of Phenom II in December 2008, while Socket AM3 versions with DDR3 support, along with an initial batch of triple- and quad-core processors were released on February 9, 2009. Dual-processor systems require Socket F+ for the Quad FX platform. The next-generation Phenom II X6 was released on April 27, 2010.

Athlon II is a family of AMD multi-core 45 nm central processing units, which is aimed at the budget to mid-range market and is a complementary product lineup to the Phenom II.

TILE-Gx was a VLIW ISA multicore processor family designed by Tilera. It consisted of a mesh network that was expected to scale up to 100 cores, but only 72-core variants actually shipped.

The IBM A2 is an open source massively multicore capable and multithreaded 64-bit Power ISA processor core designed by IBM using the Power ISA v.2.06 specification. Versions of processors based on the A2 core range from a 2.3 GHz version with 16 cores consuming 65 W to a less powerful, four core version, consuming 20 W at 1.4 GHz.

Project Denver is the codename of a central processing unit designed by Nvidia that implements the ARMv8-A 64/32-bit instruction sets using a combination of simple hardware decoder and software-based binary translation where "Denver's binary translation layer runs in software, at a lower level than the operating system, and stores commonly accessed, already optimized code sequences in a 128 MB cache stored in main memory". Denver is a very wide in-order superscalar pipeline. Its design makes it suitable for integration with other SIPs cores into one die constituting a system on a chip (SoC).

The KOMDIV-64 is a family of 64-bit microprocessors developed by the Scientific Research Institute of System Development (NIISI) of the Russian Academy of Sciences and manufactured by TSMC, UMC, GlobalFoundries, and X-Fab. The KOMDIV-64 processors are primarily intended for industrial and high-performance computing applications.

The zEC12 microprocessor is a chip made by IBM for their zEnterprise EC12 and zEnterprise BC12 mainframe computers, announced on August 28, 2012. It is manufactured at the East Fishkill, New York fabrication plant. The processor began shipping in the fall of 2012. IBM stated that it was the world's fastest microprocessor and is about 25% faster than its predecessor the z196.

The SW26010 is a 260-core manycore processor designed by the Shanghai Integrated Circuit Technology and Industry Promotion Center (Chinese: 上海集成电路技术与产业促进中心 ). It implements the Sunway architecture, a 64-bit reduced instruction set computing (RISC) architecture designed in China. The SW26010 has four clusters of 64 Compute-Processing Elements (CPEs) which are arranged in an eight-by-eight array. The CPEs support SIMD instructions and are capable of performing eight double-precision floating-point operations per cycle. Each cluster is accompanied by a more conventional general-purpose core called the Management Processing Element (MPE) that provides supervisory functions. Each cluster has its own dedicated DDR3 SDRAM controller and a memory bank with its own address space. The processor runs at a clock speed of 1.45 GHz.