This article includes a list of general references, but it lacks sufficient corresponding inline citations .(April 2009) |

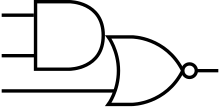

AND-OR-invert (AOI) logic and AOI gates are two-level compound (or complex) logic functions constructed from the combination of one or more AND gates followed by a NOR gate (equivalent to an OR gate through an Inverter gate, which is the "OI" part of "AOI"). Construction of AOI cells is particularly efficient using CMOS technology, where the total number of transistor gates can be compared to the same construction using NAND logic or NOR logic. The complement of AOI logic is OR-AND-invert (OAI) logic, where the OR gates precede a NAND gate. [1]