Related Research Articles

PowerPC is a reduced instruction set computer (RISC) instruction set architecture (ISA) created by the 1991 Apple–IBM–Motorola alliance, known as AIM. PowerPC, as an evolving instruction set, has been named Power ISA since 2006, while the old name lives on as a trademark for some implementations of Power Architecture–based processors.

The PowerPC 7xx is a family of third generation 32-bit PowerPC microprocessors designed and manufactured by IBM and Motorola. This family is called the PowerPC G3 by its well-known customer Apple Inc., which introduced it on November 10, 1997. The term "PowerPC G3" is often, and incorrectly, imagined to be a microprocessor when in fact a number of microprocessors from different vendors have been used. Such designations were applied to Macintosh computers such as the PowerBook G3, the multicolored iMacs, iBooks and several desktops, including both the Beige and Blue and White Power Macintosh G3s. The low power requirements and small size made the processors ideal for laptops and the name lived out its last days at Apple in the iBook.

The IBM RS64 is a family of microprocessors used in IBM's RS/6000 and AS/400 servers in the late 1990s.

The POWER5 is a microprocessor developed and fabricated by IBM. It is an improved version of the POWER4. The principal improvements are support for simultaneous multithreading (SMT) and an on-die memory controller. The POWER5 is a dual-core microprocessor, with each core supporting one physical thread and two logical threads, for a total of two physical threads and four logical threads.

The PowerPC 400 family is a line of 32-bit embedded RISC processor cores based on the PowerPC or Power ISA instruction set architectures. The cores are designed to fit inside specialized applications ranging from system-on-a-chip (SoC) microcontrollers, network appliances, application-specific integrated circuits (ASICs) and field-programmable gate arrays (FPGAs) to set-top boxes, storage devices and supercomputers.

The CVAX is a microprocessor chipset developed and fabricated by Digital Equipment Corporation (DEC) that implemented the VAX instruction set architecture (ISA). The chipset consisted of the CVAX 78034 CPU, CFPA floating-point accelerator, CVAX clock chip, and the associated support chips, the CVAX System Support Chip (CSSC), CVAX Memory Controller (CMCTL), and CVAX Q-Bus Interface Chip (CQBIC).

The transistor count is the number of transistors in an electronic device. It is the most common measure of integrated circuit complexity. The rate at which MOS transistor counts have increased generally follows Moore's law, which observed that the transistor count doubles approximately every two years. However, being directly proportional to the area of a chip, transistor count doesn't represent how advanced corresponding manufacturing technology is, which is better characterized by transistor density instead.

PowerQUICC is the name for several PowerPC- and Power ISA-based microcontrollers from Freescale Semiconductor. They are built around one or more PowerPC cores and the Communications Processor Module which is a separate RISC core specialized in such tasks such as I/O, communications, ATM, security acceleration, networking and USB. Many components are System-on-a-chip designs tailor-made for embedded applications.

The 22 nm node is the process step following 32 nm in CMOS MOSFET semiconductor device fabrication. The typical half-pitch for a memory cell using the process is around 22 nm. It was first demonstrated by semiconductor companies for use in RAM memory in 2008. In 2010, Toshiba began shipping 24 nm flash memory chips, and Samsung Electronics began mass-producing 20 nm flash memory chips. The first consumer-level CPU deliveries using a 22 nm process started in April 2012 with the Intel Ivy Bridge processors.

PWRficient is a microprocessor series by P.A. Semi where the PA6T-1682M was the only one that became an actual product.

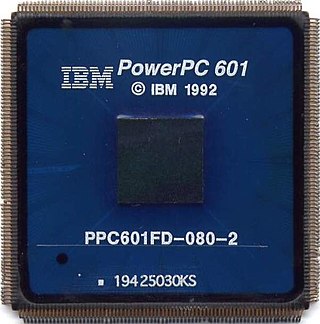

The PowerPC 600 family was the first family of PowerPC processors built. They were designed at the Somerset facility in Austin, Texas, jointly funded and staffed by engineers from IBM and Motorola as a part of the AIM alliance. Somerset was opened in 1992 and its goal was to make the first PowerPC processor and then keep designing general purpose PowerPC processors for personal computers. The first incarnation became the PowerPC 601 in 1993, and the second generation soon followed with the PowerPC 603, PowerPC 604 and the 64-bit PowerPC 620.

Intrinsity was a privately held Austin, Texas based fabless semiconductor company; it was founded in 1997 as EVSX on the remnants of Exponential Technology and changed its name to Intrinsity in 2000. It had around 100 employees and supplied tools and services for highly efficient semiconductor logic design, enabling high performance microprocessors with fewer transistors and low power consumption. The acquisition of the firm by Apple Inc. was confirmed on April 27, 2010.

The term die shrink refers to the scaling of metal-oxide-semiconductor (MOS) devices. The act of shrinking a die is to create a somewhat identical circuit using a more advanced fabrication process, usually involving an advance of lithographic nodes. This reduces overall costs for a chip company, as the absence of major architectural changes to the processor lowers research and development costs while at the same time allowing more processor dies to be manufactured on the same piece of silicon wafer, resulting in less cost per product sold.

The z10 is a microprocessor chip made by IBM for their System z10 mainframe computers, released February 26, 2008. It was called "z6" during development.

The SPARC64 V (Zeus) is a SPARC V9 microprocessor designed by Fujitsu. The SPARC64 V was the basis for a series of successive processors designed for servers, and later, supercomputers.

The IBM A2 is an open source massively multicore capable and multithreaded 64-bit Power ISA processor core designed by IBM using the Power ISA v.2.06 specification. Versions of processors based on the A2 core range from a 2.3 GHz version with 16 cores consuming 65 W to a less powerful, four core version, consuming 20 W at 1.4 GHz.

The KOMDIV-64 is a family of 64-bit microprocessors developed by the Scientific Research Institute of System Development (NIISI) of the Russian Academy of Sciences and manufactured by TSMC, UMC, GlobalFoundries, and X-Fab. The KOMDIV-64 processors are primarily intended for industrial and high-performance computing applications.

IBM Power microprocessors are designed and sold by IBM for servers and supercomputers. The name "POWER" was originally presented as an acronym for "Performance Optimization With Enhanced RISC". The Power line of microprocessors has been used in IBM's RS/6000, AS/400, pSeries, iSeries, System p, System i, and Power Systems lines of servers and supercomputers. They have also been used in data storage devices and workstations by IBM and by other server manufacturers like Bull and Hitachi.

References

- ↑ "AMCC takes another shot at multicore". EETimes. 2010-09-27. Retrieved 2011-07-14.

- ↑ "AMCC, TSMC put new MPU spin on IBM technology". EETimes. 2009-09-25. Retrieved 2011-07-14.