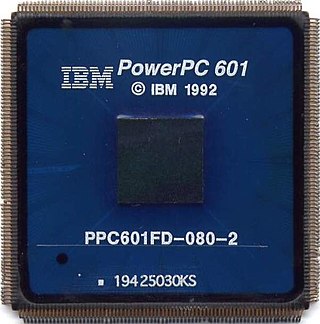

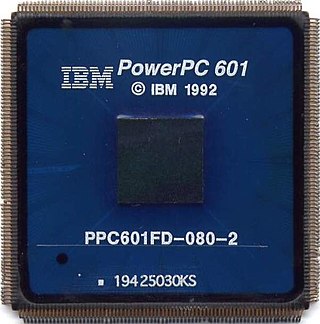

PowerPC is a reduced instruction set computer (RISC) instruction set architecture (ISA) created by the 1991 Apple–IBM–Motorola alliance, known as AIM. PowerPC, as an evolving instruction set, has been named Power ISA since 2006, while the old name lives on as a trademark for some implementations of Power Architecture–based processors.

Direct memory access (DMA) is a feature of computer systems that allows certain hardware subsystems to access main system memory independently of the central processing unit (CPU).

The Athlon 64 is a ninth-generation, AMD64-architecture microprocessor produced by Advanced Micro Devices (AMD), released on September 23, 2003. It is the third processor to bear the name Athlon, and the immediate successor to the Athlon XP. The Athlon 64 was the second processor to implement the AMD64 architecture and the first 64-bit processor targeted at the average consumer. Variants of the Athlon 64 have been produced for Socket 754, Socket 939, Socket 940, and Socket AM2. It was AMD's primary consumer CPU, and primarily competed with Intel's Pentium 4, especially the Prescott and Cedar Mill core revisions.

The Power Mac G5 is a series of personal computers designed, manufactured, and sold by Apple Computer, Inc. from 2003 to 2006 as part of the Power Mac series. When introduced, it was the most powerful computer in Apple's Macintosh lineup, and was marketed by the company as the world's first 64-bit desktop computer. It was also the first desktop computer from Apple to use an anodized aluminum alloy enclosure, and one of only three computers in Apple's lineup to utilize the PowerPC 970 CPU, the others being the iMac G5 and the Xserve G5.

The PowerPC 970, PowerPC 970FX, and PowerPC 970MP are 64-bit PowerPC CPUs from IBM introduced in 2002. Apple branded the 970 as PowerPC G5 for its Power Mac G5.

The PowerPC 400 family is a line of 32-bit embedded RISC processor cores based on the PowerPC or Power ISA instruction set architectures. The cores are designed to fit inside specialized applications ranging from system-on-a-chip (SoC) microcontrollers, network appliances, application-specific integrated circuits (ASICs) and field-programmable gate arrays (FPGAs) to set-top boxes, storage devices and supercomputers.

The AMD Family 10h, or K10, is a microprocessor microarchitecture by AMD based on the K8 microarchitecture. The first third-generation Opteron products for servers were launched on September 10, 2007, with the Phenom processors for desktops following and launching on November 11, 2007 as the immediate successors to the K8 series of processors.

Microsoft XCPU, codenamed Xenon, is a CPU used in the Xbox 360 game console, to be used with ATI's Xenos graphics chip.

P. A. Semi was an American fabless semiconductor company founded in Santa Clara, California in 2003 by Daniel W. Dobberpuhl, who was previously the lead designer for the DEC Alpha 21064 and StrongARM processors. The company employed a 150-person engineering team which included people who had previously worked on processors like Itanium, Opteron and UltraSPARC. Apple Inc acquired P.A. Semi for $278 million in April 2008.

AMD Turion is the brand name AMD applies to its x86-64 low-power consumption mobile processors codenamed K8L. The Turion 64 and Turion 64 X2/Ultra processors compete with Intel's mobile processors, initially the Pentium M and the Intel Core and Intel Core 2 processors.

AmigaOne X1000 is a PowerPC-based personal computer intended as a high-end platform for AmigaOS 4. It was announced by A-Eon Technology CVBA in partnership with Hyperion Entertainment and released in 2011. Its name pays homage to the Amiga 1000 released by Commodore in 1985. It is, however, not hardware-compatible with the original Commodore Amiga system.

The IBM A2 is an open source massively multicore capable and multithreaded 64-bit Power ISA processor core designed by IBM using the Power ISA v.2.06 specification. Versions of processors based on the A2 core range from a 2.3 GHz version with 16 cores consuming 65 W to a less powerful, four core version, consuming 20 W at 1.4 GHz.

IBM Power microprocessors are designed and sold by IBM for servers and supercomputers. The name "POWER" was originally presented as an acronym for "Performance Optimization With Enhanced RISC". The Power line of microprocessors has been used in IBM's RS/6000, AS/400, pSeries, iSeries, System p, System i, and Power Systems lines of servers and supercomputers. They have also been used in data storage devices and workstations by IBM and by other server manufacturers like Bull and Hitachi.

Since 1985, many processors implementing some version of the MIPS architecture have been designed and used widely.

Power ISA is a reduced instruction set computer (RISC) instruction set architecture (ISA) currently developed by the OpenPOWER Foundation, led by IBM. It was originally developed by IBM and the now-defunct Power.org industry group. Power ISA is an evolution of the PowerPC ISA, created by the mergers of the core PowerPC ISA and the optional Book E for embedded applications. The merger of these two components in 2006 was led by Power.org founders IBM and Freescale Semiconductor.

Apple M1 is a series of ARM-based system-on-a-chip (SoC) designed by Apple Inc., launched 2020 to 2022. It is part of the Apple silicon series, as a central processing unit (CPU) and graphics processing unit (GPU) for its Mac desktops and notebooks, and the iPad Pro and iPad Air tablets. The M1 chip initiated Apple's third change to the instruction set architecture used by Macintosh computers, switching from Intel to Apple silicon fourteen years after they were switched from PowerPC to Intel, and twenty-six years after the transition from the original Motorola 68000 series to PowerPC. At the time of its introduction in 2020, Apple said that the M1 had "the world's fastest CPU core in low power silicon" and the world's best CPU performance per watt. Its successor, Apple M2, was announced on June 6, 2022, at Worldwide Developers Conference (WWDC).

AWS Graviton is a family of 64-bit ARM-based CPUs designed by the Amazon Web Services (AWS) subsidiary Annapurna Labs. The processor family is distinguished by its lower energy use relative to x86-64, static clock rates, and lack of simultaneous multithreading. It was designed to be tightly integrated with AWS servers and datacenters, and is not sold outside Amazon.

Apple M2 is a series of ARM-based system on a chip (SoC) designed by Apple Inc., launched 2022 to 2023. It is part of the Apple silicon series, as a central processing unit (CPU) and graphics processing unit (GPU) for its Mac desktops and notebooks, the iPad Pro and iPad Air tablets, and the Vision Pro mixed reality headset. It is the second generation of ARM architecture intended for Apple's Mac computers after switching from Intel Core to Apple silicon, succeeding the M1. Apple announced the M2 on June 6, 2022, at Worldwide Developers Conference (WWDC), along with models of the MacBook Air and the 13-inch MacBook Pro using the M2. The M2 is made with TSMC's "Enhanced 5-nanometer technology" N5P process and contains 20 billion transistors, a 25% increase from the M1. Apple claims CPU improvements up to 18% and GPU improvements up to 35% compared to the M1.