In digital logic, an inverter or NOT gate is a logic gate which implements logical negation. It outputs a bit opposite of the bit that is put into it. The bits are typically implemented as two differing voltage levels.

In digital logic, an inverter or NOT gate is a logic gate which implements logical negation. It outputs a bit opposite of the bit that is put into it. The bits are typically implemented as two differing voltage levels.

| Inverter truth table | |

|---|---|

| Input | Output |

| A | NOT A |

| 0 | 1 |

| 1 | 0 |

The NOT gate outputs a zero when given a one, and a one when given a zero. Hence, it inverts its inputs. Colloquially, this inversion of bits is called "flipping" bits. [1] As with all binary logic gates, other pairs of symbols — such as true and false, or high and low — may be used in lieu of one and zero.

It is equivalent to the logical negation operator (¬) in mathematical logic. Because it has only one input, it is a unary operation and has the simplest type of truth table. It is also called the complement gate [2] because it produces the ones' complement of a binary number, swapping 0s and 1s.

The NOT gate is one of three basic logic gates from which any Boolean circuit may be built up. Together with the AND gate and the OR gate, any function in binary mathematics may be implemented. All other logic gates may be made from these three. [3]

The terms "programmable inverter" or "controlled inverter" do not refer to this gate; instead, these terms refer to the XOR gate because it can conditionally function like a NOT gate. [1] [3]

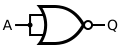

The traditional symbol for an inverter circuit is a triangle touching a small circle or "bubble". Input and output lines are attached to the symbol; the bubble is typically attached to the output line. To symbolize active-low input, sometimes the bubble is instead placed on the input line. [4] Sometimes only the circle portion of the symbol is used, and it is attached to the input or output of another gate; the symbols for NAND and NOR are formed in this way. [3]

A bar or overline ( ‾ ) above a variable can denote negation (or inversion or complement) performed by a NOT gate. [4] A slash (/) before the variable is also used. [3]

An inverter circuit outputs a voltage representing the opposite logic-level to its input. Its main function is to invert the input signal applied. If the applied input is low then the output becomes high and vice versa. Inverters can be constructed using a single NMOS transistor or a single PMOS transistor coupled with a resistor. Since this "resistive-drain" approach uses only a single type of transistor, it can be fabricated at a low cost. However, because current flows through the resistor in one of the two states, the resistive-drain configuration is disadvantaged for power consumption and processing speed. Alternatively, inverters can be constructed using two complementary transistors in a CMOS configuration. This configuration greatly reduces power consumption since one of the transistors is always off in both logic states. [5] Processing speed can also be improved due to the relatively low resistance compared to the NMOS-only or PMOS-only type devices. Inverters can also be constructed with bipolar junction transistors (BJT) in either a resistor–transistor logic (RTL) or a transistor–transistor logic (TTL) configuration.

Digital electronics circuits operate at fixed voltage levels corresponding to a logical 0 or 1 (see binary). An inverter circuit serves as the basic logic gate to swap between those two voltage levels. Implementation determines the actual voltage, but common levels include (0, +5V) for TTL circuits.

The inverter is a basic building block in digital electronics. Multiplexers, decoders, state machines, and other sophisticated digital devices may use inverters.

The hex inverter is an integrated circuit that contains six ( hexa- ) inverters. For example, the 7404 TTL chip which has 14 pins and the 4049 CMOS chip which has 16 pins, 2 of which are used for power/referencing, and 12 of which are used by the inputs and outputs of the six inverters (the 4049 has 2 pins with no connection).

is the analytical representation of NOT gate:

If no specific NOT gates are available, one can be made from the universal NAND or NOR gates, [6] an XOR gate by setting one input to high or an XNOR gate by setting one input to low.

| Desired gate | NAND construction | NOR construction |

|---|---|---|

|  |  |

Digital inverter quality is often measured using the voltage transfer curve (VTC), which is a plot of output vs. input voltage. From such a graph, device parameters including noise tolerance, gain, and operating logic levels can be obtained.

Ideally, the VTC appears as an inverted step function – this would indicate precise switching between on and off – but in real devices, a gradual transition region exists. The VTC indicates that for low input voltage, the circuit outputs high voltage; for high input, the output tapers off towards the low level. The slope of this transition region is a measure of quality – steep (close to vertical) slopes yield precise switching.

The tolerance to noise can be measured by comparing the minimum input to the maximum output for each region of operation (on / off).

Since the transition region is steep and approximately linear, a properly-biased CMOS inverter digital logic gate may be used as a high-gain analog linear amplifier [7] [8] [9] [10] [11] or even combined to form an opamp. [12] Maximum gain is achieved when the input and output operating points are the same voltage, which can be biased by connecting a resistor between the output and input. [13]