AVR is a family of microcontrollers developed since 1996 by Atmel, acquired by Microchip Technology in 2016. These are modified Harvard architecture 8-bit RISC single-chip microcontrollers. AVR was one of the first microcontroller families to use on-chip flash memory for program storage, as opposed to one-time programmable ROM, EPROM, or EEPROM used by other microcontrollers at the time.

The 68HC12 is a microcontroller family from Motorola Semiconductor. Originally introduced in the mid-1990s, the architecture is an enhancement of the Freescale 68HC11. Programs written for the HC11 are usually compatible with the HC12, which has a few extra instructions. The first 68HC12 derivatives had a maximum bus speed of 8 MHz and flash memory sizes up to 128 KB.

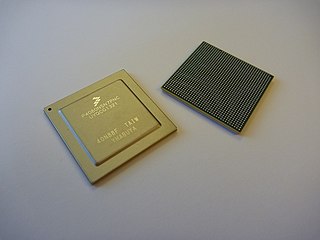

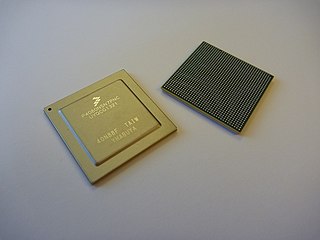

The MPC5xx family of processors such as the MPC555 and MPC565 are 32-bit PowerPC embedded microprocessors that operate between 40 and 66 MHz and are frequently used in automotive applications including engine and transmission controllers. Delphi Corporation use either the MPC561 or MPC565 in the engine controllers they supply to General Motors, with nearly all 2009 model GM North America vehicles now using an MPC5xx in the engine controller. Bosch also used the MPC5xx throughout the ME(D)-9 series of Gasoline Engine Controllers, EDC-16 series of Diesel Engine Controllers as did the Cummins B series diesel engine ECU.

The PowerPC 400 family is a line of 32-bit embedded RISC processor cores based on the PowerPC or Power ISA instruction set architectures. The cores are designed to fit inside specialized applications ranging from system-on-a-chip (SoC) microcontrollers, network appliances, application-specific integrated circuits (ASICs) and field-programmable gate arrays (FPGAs) to set-top boxes, storage devices and supercomputers.

The XGameStation is a series of embedded systems, primarily designed as a dedicated home video game console, created by Andre LaMothe and sold by his company Nurve Networks LLC. Originally designed to teach electronics and video game development to programmers, newer models concentrate more on logic design, multi-core programming, game programming, and embedded system design and programming with popular microcontrollers.

The Apple Network Server (ANS) was a line of PowerPC-based server computers designed, manufactured and sold by Apple Computer, Inc. from February 1996 to April 1997. It was codenamed "Shiner" and originally consisted of two models, the Network Server 500/132 and the Network Server 700/150, which got a companion model, the Network Server 700/200 with a faster CPU in November 1996.

PowerQUICC is the name for several PowerPC- and Power ISA-based microcontrollers from Freescale Semiconductor. They are built around one or more PowerPC cores and the Communications Processor Module which is a separate RISC core specialized in such tasks such as I/O, communications, ATM, security acceleration, networking and USB. Many components are System-on-a-chip designs tailor-made for embedded applications.

Efika is a line of power efficient ARM architecture and Power ISA based computers manufactured by Genesi.

The PowerPC e200 is a family of 32-bit Power ISA microprocessor cores developed by Freescale for primary use in automotive and industrial control systems. The cores are designed to form the CPU part in system-on-a-chip (SoC) designs with speed ranging up to 600 MHz, thus making them ideal for embedded applications.

The PowerPC e600 is a family of 32-bit PowerPC microprocessor cores developed by Freescale for primary use in high performance system-on-a-chip (SoC) designs with speed ranging over 2 GHz, thus making them ideal for high performance routing and telecommunications applications. The e600 is the continuation of the PowerPC 74xx design.

The i.MX range is a family of NXP proprietary microprocessors dedicated to multimedia applications based on the ARM architecture and focused on low-power consumption. The i.MX application processors are SoCs (System-on-Chip) that integrate many processing units into one die, like the main CPU, a video processing unit, and a graphics processing unit for instance. The i.MX products are qualified for automotive, industrial, and consumer markets. Most of them are guaranteed for a production lifetime of 10 to 15 years.

QorIQ is a brand of ARM-based and Power ISA–based communications microprocessors from NXP Semiconductors. It is the evolutionary step from the PowerQUICC platform, and initial products were built around one or more e500mc cores and came in five different product platforms, P1, P2, P3, P4, and P5, segmented by performance and functionality. The platform keeps software compatibility with older PowerPC products such as the PowerQUICC platform. In 2012 Freescale announced ARM-based QorIQ offerings beginning in 2013.

STM32 is a family of 32-bit microcontroller integrated circuits by STMicroelectronics. The STM32 chips are grouped into related series that are based around the same 32-bit ARM processor core: Cortex-M0, Cortex-M0+, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M33. Internally, each microcontroller consists of ARM processor core(s), flash memory, static RAM, debugging interface, and various peripherals.

LPC is a family of 32-bit microcontroller integrated circuits by NXP Semiconductors. The LPC chips are grouped into related series that are based around the same 32-bit ARM processor core, such as the Cortex-M4F, Cortex-M3, Cortex-M0+, or Cortex-M0. Internally, each microcontroller consists of the processor core, static RAM memory, flash memory, debugging interface, and various peripherals. The earliest LPC series were based on the Intel 8-bit 80C51 core. As of February 2011, NXP had shipped over one billion ARM processor-based chips.

Intel Quark is a line of 32-bit x86 SoCs and microcontrollers by Intel, designed for small size and low power consumption, and targeted at new markets including wearable devices. The line was introduced at Intel Developer Forum in 2013, and discontinued in January 2019.

Qorivva is a line of Power ISA 2.03-based microcontrollers from Freescale built around one or more PowerPC e200 cores. Within this line are a number of products specifically targeted for functional safety applications. The hardware-based fault detection and correction features found within this line include dual cores that may run in lock-step, full-path ECC, automated self-testing of memory and logic, peripheral redundancy, and monitor/checker cores.

The MSP432 is a mixed-signal microcontroller family from Texas Instruments. It is based on a 32-bit ARM Cortex-M4F CPU, and extends their 16-bit MSP430 line, with a larger address space for code and data, and faster integer and floating point calculation than the MSP430. Like the MSP430, it has a number of built-in peripheral devices, and is designed for low power requirements. In 2021, TI confirmed that the MSP432 has been discontinued and "there will be no new MSP432 products".