In telecommunications, RS-232 or Recommended Standard 232 is a standard originally introduced in 1960 for serial communication transmission of data. It formally defines signals connecting between a DTE such as a computer terminal, and a DCE, such as a modem. The standard defines the electrical characteristics and timing of signals, the meaning of signals, and the physical size and pinout of connectors. The current version of the standard is TIA-232-F Interface Between Data Terminal Equipment and Data Circuit-Terminating Equipment Employing Serial Binary Data Interchange, issued in 1997. The RS-232 standard had been commonly used in computer serial ports and is still widely used in industrial communication devices.

Automatic baud rate detection refers to the process by which a receiving device determines the speed, code level, start bit, and stop bits of incoming data by examining the first character, usually a preselected sign-on character (syncword) on a UART connection. ABR allows the receiving device to accept data from a variety of transmitting devices operating at different speeds without needing to establish data rates in advance.

A universal asynchronous receiver-transmitter is a computer hardware device for asynchronous serial communication in which the data format and transmission speeds are configurable. It sends data bits one by one, from the least significant to the most significant, framed by start and stop bits so that precise timing is handled by the communication channel. The electric signaling levels are handled by a driver circuit external to the UART. Two common signal levels are RS-232, a 12-volt system, and RS-485, a 5-volt system. Early teletypewriters used current loops.

In computing, a serial port is a serial communication interface through which information transfers in or out sequentially one bit at a time. This is in contrast to a parallel port, which communicates multiple bits simultaneously in parallel. Throughout most of the history of personal computers, data has been transferred through serial ports to devices such as modems, terminals, various peripherals, and directly between computers.

COM is the original, yet still common, name of the serial port interface on PC-compatible computers. It can refer not only to physical ports, but also to emulated ports, such as ports created by Bluetooth or USB adapters.

Asynchronous serial communication is a form of serial communication in which the communicating endpoints' interfaces are not continuously synchronized by a common clock signal. Instead of a common synchronization signal, the data stream contains synchronization information in form of start and stop signals, before and after each unit of transmission, respectively. The start signal prepares the receiver for arrival of data and the stop signal resets its state to enable triggering of a new sequence.

The IBM Personal Computer/AT was released in 1984 as the fourth model in the IBM Personal Computer line, following the IBM PC/XT and its IBM Portable PC variant. It was designed around the Intel 80286 microprocessor.

The 6551Asynchronous Communications Interface Adapter (ACIA) was an integrated circuit made by MOS Technology. It served as a companion UART chip for the widely popular 6502 microprocessor. Intended to implement RS-232, its specifications called for a maximum speed of 19,200 bits per second with its onboard baud-rate generator, or 125kbit/s using an external 16x clock.

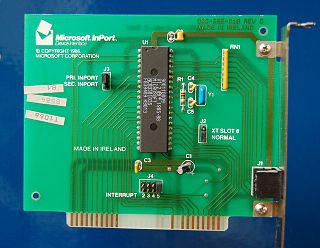

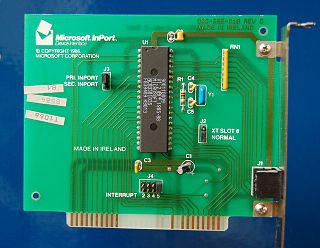

A bus mouse is a variety of PC computer mouse which is attached to the computer using a specialized interface.

A universal synchronous and asynchronous receiver-transmitter is a type of a serial interface device that can be programmed to communicate asynchronously or synchronously. See universal asynchronous receiver-transmitter (UART) for a discussion of the asynchronous capabilities of these devices.

Double Data Rate 3 Synchronous Dynamic Random-Access Memory is a type of synchronous dynamic random-access memory (SDRAM) with a high bandwidth interface, and has been in use since 2007. It is the higher-speed successor to DDR and DDR2 and predecessor to DDR4 synchronous dynamic random-access memory (SDRAM) chips. DDR3 SDRAM is neither forward nor backward compatible with any earlier type of random-access memory (RAM) because of different signaling voltages, timings, and other factors.

The Hyperion is an early portable computer that vied with the Compaq Portable to be the first portable IBM PC compatible. It was marketed by Infotech Cie of Ottawa, a subsidiary of Bytec Management Corp., who acquired the designer and manufacturer Dynalogic in January 1983. In 1984 the design was licensed by Commodore International in a move that was forecast as a "radical shift of position" and a signal that Commodore would soon dominate the PC compatible market. Despite computers being "hand-assembled from kits" provided by Bytec and displayed alongside the Commodore 900 at a German trade show as their forthcoming first portable computer, it was never sold by Commodore and some analysts downplayed the pact. The Hyperion was shipped in January 1983 at C$4995, two months ahead of the Compaq Portable.

The 8250 UART is an integrated circuit designed for implementing the interface for serial communications. The part was originally manufactured by the National Semiconductor Corporation. It was commonly used in PCs and related equipment such as printers or modems. The 8250 included an on-chip programmable bit rate generator, allowing use for both common and special-purpose bit rates which could be accurately derived from an arbitrary crystal oscillator reference frequency.

The Western Design Center (WDC) W65C134S is an 8-bit CMOS microcontroller based on a W65C02S processor core, which is a superset of the MOS Technology 6502 processor.

The AAA chipset was intended to be the next-generation Amiga multimedia system designed by Commodore International. Initially begun as a secret project, the first design discussions were started in 1988, and after many revisions and redesigns the first silicon versions were fabricated in 1992–1993. The project was all but abandoned in 1993 after it was projected that PCs were to equal the AAA shortly after release, so a further jump was needed, leading to project Hombre. AAA was not designed to be AGA compatible.

Intel 8237 is a direct memory access (DMA) controller, a part of the MCS 85 microprocessor family. It enables data transfer between memory and the I/O with reduced load on the system's main processor by providing the memory with control signals and memory address information during the DMA transfer.

The SCC, short for Serial Communication Controller, is a family of serial port driver integrated circuits made by Zilog. The primary members of the family are the Z8030/Z8530, and the Z85233.

In computing, a keyboard controller is a device that interfaces a keyboard to a computer. Its main function is to inform the computer when a key is pressed or released. When data from the keyboard arrives, the controller raises an interrupt to allow the CPU to handle the input.

Interrupt coalescing, also known as interrupt moderation, is a technique in which events which would normally trigger a hardware interrupt are held back, either until a certain amount of work is pending, or a timeout timer triggers. Used correctly, this technique can reduce interrupt load by up to an order of magnitude, while only incurring relatively small latency penalties. Interrupt coalescing is typically combined with either a hardware FIFO or direct memory access, to allow for continued data throughput while interrupts are being held back.