ARM is a family of RISC instruction set architectures (ISAs) for computer processors. Arm Holdings develops the ISAs and licenses them to other companies, who build the physical devices that use the instruction set. It also designs and licenses cores that implement these ISAs.

AVR is a family of microcontrollers developed since 1996 by Atmel, acquired by Microchip Technology in 2016. These are modified Harvard architecture 8-bit RISC single-chip microcontrollers. AVR was one of the first microcontroller families to use on-chip flash memory for program storage, as opposed to one-time programmable ROM, EPROM, or EEPROM used by other microcontrollers at the time.

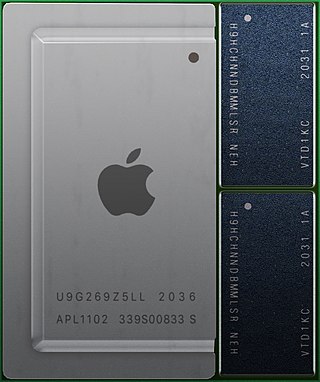

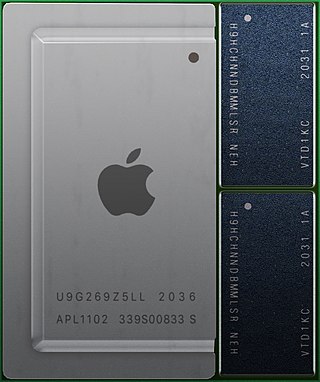

A system on a chip or system-on-chip is an integrated circuit that integrates most or all components of a computer or other electronic system. These components almost always include on-chip central processing unit (CPU), memory interfaces, input/output devices and interfaces, and secondary storage interfaces, often alongside other components such as radio modems and a graphics processing unit (GPU) – all on a single substrate or microchip. SoCs may contain digital and also analog, mixed-signal and often radio frequency signal processing functions.

JTAG is an industry standard for verifying designs of and testing printed circuit boards after manufacture.

The MicroBlaze is a soft microprocessor core designed for Xilinx field-programmable gate arrays (FPGA). As a soft-core processor, MicroBlaze is implemented entirely in the general-purpose memory and logic fabric of Xilinx FPGAs.

Atmel ARM-based processors are microcontrollers and microprocessors integrated circuits, by Microchip Technology, that are based on various 32-bit ARM processor cores, with in-house designed peripherals and tool support.

ARM9 is a group of 32-bit RISC ARM processor cores licensed by ARM Holdings for microcontroller use. The ARM9 core family consists of ARM9TDMI, ARM940T, ARM9E-S, ARM966E-S, ARM920T, ARM922T, ARM946E-S, ARM9EJ-S, ARM926EJ-S, ARM968E-S, ARM996HS. ARM9 cores were released from 1998 to 2006 and they are no longer recommended for new IC designs; recommended alternatives include ARM Cortex-A, ARM Cortex-M, and ARM Cortex-R cores.

The Open Core Protocol (OCP) is a protocol for on-chip subsystem communications. It is an openly licensed, core-centric protocol and defines a bus-independent, configurable interface. OCP International Partnership (OCP-IP) produces OCP specifications. OCP data transfer models range from simple request-grant handshaking through pipelined request-response to complex out-of-order operations.

EFM32 Gecko MCUs are a family of mixed-signal 32-bit microcontroller integrated circuits from Energy Micro based on ARM Cortex-M CPUs, including the Cortex-M0+, Cortex-M3, and Cortex-M4.

eSi-RISC is a configurable CPU architecture. It is available in five implementations: the eSi-1600, eSi-1650, eSi-3200, eSi-3250 and eSi-3264. The eSi-1600 and eSi-1650 feature a 16-bit data-path, while the eSi-32x0s feature 32-bit data-paths, and the eSi-3264 features a mixed 32/64-bit datapath. Each of these processors is licensed as soft IP cores, suitable for integrating into both ASICs and FPGAs.

The ARM Cortex-A15 MPCore is a 32-bit processor core licensed by ARM Holdings implementing the ARMv7-A architecture. It is a multicore processor with out-of-order superscalar pipeline running at up to 2.5 GHz.

The ARM Cortex-M is a group of 32-bit RISC ARM processor cores licensed by ARM Limited. These cores are optimized for low-cost and energy-efficient integrated circuits, which have been embedded in tens of billions of consumer devices. Though they are most often the main component of microcontroller chips, sometimes they are embedded inside other types of chips too. The Cortex-M family consists of Cortex-M0, Cortex-M0+, Cortex-M1, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M23, Cortex-M33, Cortex-M35P, Cortex-M52, Cortex-M55, Cortex-M85. A floating-point unit (FPU) option is available for Cortex-M4 / M7 / M33 / M35P / M52 / M55 / M85 cores, and when included in the silicon these cores are sometimes known as "Cortex-MxF", where 'x' is the core variant.

STM32 is a family of 32-bit microcontroller integrated circuits by STMicroelectronics. The STM32 chips are grouped into related series that are based around the same 32-bit ARM processor core: Cortex-M0, Cortex-M0+, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M33. Internally, each microcontroller consists of ARM processor core(s), flash memory, static RAM, debugging interface, and various peripherals.

XMC is a family of microcontroller ICs by Infineon. The XMC microcontrollers use the 32-bit RISC ARM processor cores from ARM Holdings, such as Cortex-M4F and Cortex-M0. XMC stands for "cross-market microcontrollers", meaning that this family can cover due to compatibility and configuration options, a wide range in industrial applications. The family supports three essential trends in the industry: It increases the energy efficiency of the systems, supports a variety of communication standards and reduces software complexity in the development of the application's software environment with the parallel released eclipse-based software tool DAVE.

LPC is a family of 32-bit microcontroller integrated circuits by NXP Semiconductors. The LPC chips are grouped into related series that are based around the same 32-bit ARM processor core, such as the Cortex-M4F, Cortex-M3, Cortex-M0+, or Cortex-M0. Internally, each microcontroller consists of the processor core, static RAM memory, flash memory, debugging interface, and various peripherals. The earliest LPC series were based on the Intel 8-bit 80C51 core. As of February 2011, NXP had shipped over one billion ARM processor-based chips.

VisualSim Architect is an electronic system-level software for modeling and simulation of electronic systems, embedded software, and semiconductors. VisualSim Architect is a commercial version of the Ptolemy II research project at the University of California Berkeley. The product was first released in 2003. VisualSim is a graphical tool that can be used for performance trade-off analyses using such metrics as bandwidth utilization, application response time, and buffer requirements. It can be used for architectural analysis of algorithms, components, software instructions, and hardware/software partitioning.

In computing, autonomous peripheral operation is a hardware feature found in some microcontroller architectures to off-load certain tasks into embedded autonomous peripherals in order to minimize latencies and improve throughput in hard real-time applications as well as to save energy in ultra-low-power designs.

The Advanced eXtensible Interface (AXI) is an on-chip communication bus protocol and is part of the Advanced Microcontroller Bus Architecture specification (AMBA). AXI had been introduced in 2003 with the AMBA3 specification. In 2010, a new revision of AMBA, AMBA4, defined the AXI4, AXI4-Lite and AXI4-Stream protocols. AXI is royalty-free and its specification is freely available from ARM.

The ARM Neoverse is a group of 64-bit ARM processor cores licensed by Arm Holdings. The cores are intended for datacenter, edge computing, and high-performance computing use. The group consists of ARM Neoverse V-Series, ARM Neoverse N-Series, and ARM Neoverse E-Series.