Advanced Micro Devices, Inc. (AMD) is a multinational semiconductor company based in Santa Clara County, California that develops computer processors and related technologies for business and consumer markets. While initially it manufactured its own processors, the company later outsourced its manufacturing, a practice known as going fabless, after GlobalFoundries was spun off in 2009. AMD's main products include microprocessors, motherboard chipsets, embedded processors and graphics processors for servers, workstations, personal computers and embedded system applications.

The AMD Accelerated Processing Unit (APU), formerly known as Fusion, is the marketing term for a series of 64-bit microprocessors from Advanced Micro Devices (AMD), designed to act as a central processing unit (CPU) and graphics processing unit (GPU) on a single die. APUs are general purpose processors that feature nearly discrete integrated graphics processors (IGPs), which generally are a class above what would normally be termed as "integrated" graphics.

Unified Video Decoder (UVD), previously called Universal Video Decoder, is the name given to AMD's dedicated video decoding ASIC. There are multiple versions implementing a multitude of video codecs, such as H.264 and VC-1.

AMD PowerPlay is the brand name for a set of technologies for the reduction of the energy consumption implemented in several of AMD's graphics processing units and APUs supported by their proprietary graphics device driver "Catalyst". AMD PowerPlay is also implemented into ATI/AMD chipsets which integrated graphics and into AMD's Imageon handheld chipset, that was sold to Qualcomm in 2008.

The Socket FS1 is for notebooks using AMD APU processors codenamed Llano, Trinity and Richland.

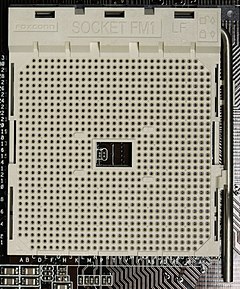

Socket FM2 is a CPU socket used by AMD's desktop Trinity and Richland APUs to connect to the motherboard as well as Athlon X2 and Athlon X4 processors based on them. FM2 was launched on September 27, 2012. Motherboards which feature the at the time new FM2 CPU socket also utilize AMD's at the time new A85X chipset.

Heterogeneous System Architecture (HSA) is a cross-vendor set of specifications that allow for the integration of central processing units and graphics processors on the same bus, with shared memory and tasks. The HSA is being developed by the HSA Foundation, which includes AMD and ARM. The platform's stated aim is to reduce communication latency between CPUs, GPUs and other compute devices, and make these various devices more compatible from a programmer's perspective, relieving the programmer of the task of planning the moving of data between devices' disjoint memories.

AMD Excavator Family 15h is a microarchitecture developed by AMD to succeed Steamroller Family 15h for use in AMD APU processors and normal CPUs. On October 12, 2011, AMD revealed Excavator to be the code name for the fourth-generation Bulldozer-derived core.

Socket FM2+ (FM2b) is a CPU socket used by AMD's desktop "Kaveri" APUs (Steamroller-based) and Godavari APUs (Steamroller-based) to connect to the motherboard. The FM2+ has a slightly different pin configuration to Socket FM2 with two additional pin sockets. Socket FM2+ APUs are not compatible with Socket FM2 motherboards due to the aforementioned additional pins. However, socket FM2 APUs such as "Richland" and "Trinity" are compatible with the FM2+ socket.

Video Code Engine is AMD's video encoding ASIC implementing the video codec H.264/MPEG-4 AVC. Since 2012 it is integrated into all of their GPUs and APUs except Oland.

AMD Eyefinity is a brand name for AMD video card products that support multi-monitor setups by integrating multiple display controllers on one GPU. AMD Eyefinity was introduced with the Radeon HD 5000 Series "Evergreen" in September 2009 and has been available on APUs and professional-grade graphics cards branded AMD FirePro as well.

AMD's Socket FT3 or BGA-769 targets mobile devices and was designed for APUs codenamed Kabini and Temash, Beema and Mullins.

The Socket FT1 or BGA413 is a CPU socket released in January 2011 from AMD for its APUs codenamed Desna, Ontario, Zacate and Hondo. The uber name is "Brazos".

The Socket FP2 or µBGA-827 is a CPU socket for notebooks that was released in May 2012 by AMD with its APU processors codenamed Trinity and Richland.

The Socket FP3 or µBGA906 is a CPU socket for laptops that was released in June 2014 by AMD with its mobility APU products codenamed Kaveri.

AMD PowerTune is a series of dynamic frequency scaling technologies built into some AMD GPUs and APUs that allow the clock speed of the processor to be dynamically changed by software. This allows the processor to meet the instantaneous performance needs of the operation being performed, while minimizing power draw, heat generation and noise avoidance. AMD PowerTune aims to solve thermal design power and performance constraints.

Ryzen is a brand of x86-64 microprocessors designed and marketed by Advanced Micro Devices, Inc. (AMD) for desktop, mobile and embedded platforms based on the Zen microarchitecture and its successors. It consists of central processing units marketed for mainstream, enthusiast and workstation segments and accelerated processing units (APUs) marketed for mainstream and entry-level segments and embedded applications. Ryzen is especially significant for AMD, since it is a completely new design, and since it marks the corporation's return to the high end desktop CPU market. AMD's competitor Intel has controlled this section of the market for almost ten years, back when Intel released the Conroe/Core microarchitecture, which overtook AMD's Athlon 64 as the cutting edge of performance in the market.

The Radeon RX Vega series is a series of graphics processors developed by AMD. These GPUs use the Graphics Core Next (GCN) 5th generation architecture, codenamed Vega, and are manufactured on 14 nm FinFET technology, developed by Samsung Electronics and licensed to GlobalFoundries. The series consists of desktop graphics cards and APUs aimed at desktops, mobile devices, and embedded applications.