Related Research Articles

ARM is a family of RISC instruction set architectures (ISAs) for computer processors. Arm Ltd. develops the ISAs and licenses them to other companies, who build the physical devices that use the instruction set. It also designs and licenses cores that implement these ISAs.

SuperH is a 32-bit reduced instruction set computing (RISC) instruction set architecture (ISA) developed by Hitachi and currently produced by Renesas. It is implemented by microcontrollers and microprocessors for embedded systems.

OpenRISC is a project to develop a series of open-source hardware based central processing units (CPUs) on established reduced instruction set computer (RISC) principles. It includes an instruction set architecture (ISA) using an open-source license. It is the original flagship project of the OpenCores community.

The NXP ColdFire is a microprocessor that derives from the Motorola 68000 family architecture, manufactured for embedded systems development by NXP Semiconductors. It was formerly manufactured by Freescale Semiconductor which merged with NXP in 2015.

The Blackfin is a family of 16-/32-bit microprocessors developed, manufactured and marketed by Analog Devices. The processors have built-in, fixed-point digital signal processor (DSP) functionality performed by 16-bit multiply–accumulates (MACs), accompanied on-chip by a microcontroller. It was designed for a unified low-power processor architecture that can run operating systems while simultaneously handling complex numeric tasks such as real-time H.264 video encoding.

LEON is a radiation-tolerant 32-bit central processing unit (CPU) microprocessor core that implements the SPARC V8 instruction set architecture (ISA) developed by Sun Microsystems. It was originally designed by the European Space Research and Technology Centre (ESTEC), part of the European Space Agency (ESA), without any involvement by Sun. Later versions have been designed by Gaisler Research, under a variety of owners. It is described in synthesizable VHSIC Hardware Description Language (VHDL). LEON has a dual license model: An GNU Lesser General Public License (LGPL) and GNU General Public License (GPL) free and open-source software (FOSS) license that can be used without licensing fee, or a proprietary license that can be purchased for integration in a proprietary product. The core is configurable through VHDL generics, and is used in system on a chip (SOC) designs both in research and commercial settings.

Nios II is a 32-bit embedded processor architecture designed specifically for the Altera family of field-programmable gate array (FPGA) integrated circuits. Nios II incorporates many enhancements over the original Nios architecture, making it more suitable for a wider range of embedded computing applications, from digital signal processing (DSP) to system-control.

The MicroBlaze is a soft microprocessor core designed for Xilinx field-programmable gate arrays (FPGA). As a soft-core processor, MicroBlaze is implemented entirely in the general-purpose memory and logic fabric of Xilinx FPGAs.

Alchemy is a family of ultra low power embedded microprocessors originally designed by Alchemy Semiconductor for communication and media devices. Alchemy processors are SoCs integrating a CPU core, a memory controller, and a varying set of peripherals. All members of the family use the Au1 CPU core implementing the MIPS32 instruction set by MIPS Technologies.

V850 is a 32-bit RISC CPU architecture produced by Renesas Electronics for embedded microcontrollers. It was designed by NEC as a replacement for their earlier NEC V60 family, and was introduced shortly before NEC sold their designs to Renesas in the early 1990s. It has continued to be developed by Renesas as of 2018.

The XAP processor uses a RISC processor architecture, developed by Cambridge Consultants. XAP processors have 16-bit and 32-bit cores, all of which are intended for use in an application-specific integrated circuit or ASIC chip design. They are designed for use in mixed-signal integrated circuits for sensor or wireless applications including Bluetooth, Zigbee, GPS, RFID or Near Field Communication chips. Typically, these integrated circuits are used in low-cost, high-volume products that are battery-powered and must have low energy consumption. There are other applications where XAP processors have been used to good effect, such as wireless sensor networks and medical devices, e.g. hearing aids. XAP processors, with their robust architecture and efficient power usage, are well-suited for deployment in space applications, where reliability and endurance against harsh conditions are paramount.

The LatticeMico8 is an 8-bit microcontroller reduced instruction set computer (RISC) soft processor core optimized for field-programmable gate arrays (FPGAs) and crossover programmable logic device architecture from Lattice Semiconductor. Combining a full 18-bit wide instruction set with 32 general purpose registers, the LatticeMico8 is a flexible Verilog reference design suitable for a wide variety of markets, including communications, consumer, computer, medical, industrial, and automotive. The core consumes minimal device resources, less than 200 lookup tables (LUTs) in the smallest configuration, while maintaining a broad feature set.

The NEC V60 is a CISC microprocessor manufactured by NEC starting in 1986. Several improved versions were introduced with the same instruction set architecture (ISA), the V70 in 1987, and the V80 and AFPP in 1989. They were succeeded by the V800 product families, which is currently produced by Renesas Electronics.

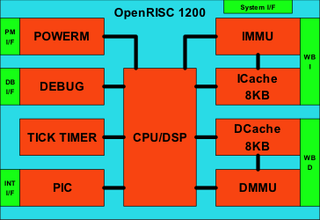

The OpenRISC 1200 (OR1200) is an implementation of the open source OpenRISC 1000 RISC architecture.

eSi-RISC is a configurable CPU architecture. It is available in five implementations: the eSi-1600, eSi-1650, eSi-3200, eSi-3250 and eSi-3264. The eSi-1600 and eSi-1650 feature a 16-bit data-path, while the eSi-32x0s feature 32-bit data-paths, and the eSi-3264 features a mixed 32/64-bit datapath. Each of these processors is licensed as soft IP cores, suitable for integrating into both ASICs and FPGAs.

M-Labs is a company which develops, manufactures and sells open hardware devices and software. It is known for the Milkymist System-On-Chip (SoC) which is a commercialized system-on-chip with free HDL source code.

The Amber processor core is an ARM architecture-compatible 32-bit reduced instruction set computing (RISC) processor. It is open source, hosted on the OpenCores website, and is part of a movement to develop a library of open source hardware projects.

RISC-V is an open standard instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles. Unlike most other ISA designs, RISC-V is provided under royalty-free open-source licenses. Many companies are offering or have announced RISC-V hardware; open source operating systems with RISC-V support are available, and the instruction set is supported in several popular software toolchains.

The ZPU is a microprocessor stack machine designed by Norwegian company Zylin AS to run supervisory code in electronic systems that include a field-programmable gate array (FPGA).

References

- ↑ "AMD x86 SMU firmware analysis". 2014-12-27.