Computer memory stores information, such as data and programs, for immediate use in the computer. The term memory is often synonymous with the terms RAM,main memory, or primary storage. Archaic synonyms for main memory include core and store.

Double Data Rate Synchronous Dynamic Random-Access Memory is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) class of memory integrated circuits used in computers. DDR SDRAM, also retroactively called DDR1 SDRAM, has been superseded by DDR2 SDRAM, DDR3 SDRAM, DDR4 SDRAM and DDR5 SDRAM. None of its successors are forward or backward compatible with DDR1 SDRAM, meaning DDR2, DDR3, DDR4 and DDR5 memory modules will not work on DDR1-equipped motherboards, and vice versa.

Flash memory is an electronic non-volatile computer memory storage medium that can be electrically erased and reprogrammed. The two main types of flash memory, NOR flash and NAND flash, are named for the NOR and NAND logic gates. Both use the same cell design, consisting of floating gate MOSFETs. They differ at the circuit level depending on whether the state of the bit line or word lines is pulled high or low: in NAND flash, the relationship between the bit line and the word lines resembles a NAND gate; in NOR flash, it resembles a NOR gate.

Static random-access memory is a type of random-access memory (RAM) that uses latching circuitry (flip-flop) to store each bit. SRAM is volatile memory; data is lost when power is removed.

Synchronous dynamic random-access memory is any DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal.

Bubble memory is a type of non-volatile computer memory that uses a thin film of a magnetic material to hold small magnetized areas, known as bubbles or domains, each storing one bit of data. The material is arranged to form a series of parallel tracks that the bubbles can move along under the action of an external magnetic field. The bubbles are read by moving them to the edge of the material, where they can be read by a conventional magnetic pickup, and then rewritten on the far edge to keep the memory cycling through the material. In operation, bubble memories are similar to delay-line memory systems.

Non-volatile random-access memory (NVRAM) is random-access memory that retains data without applied power. This is in contrast to dynamic random-access memory (DRAM) and static random-access memory (SRAM), which both maintain data only for as long as power is applied, or forms of sequential-access memory such as magnetic tape, which cannot be randomly accessed but which retains data indefinitely without electric power.

Magnetoresistive random-access memory (MRAM) is a type of non-volatile random-access memory which stores data in magnetic domains. Developed in the mid-1980s, proponents have argued that magnetoresistive RAM will eventually surpass competing technologies to become a dominant or even universal memory. Currently, memory technologies in use such as flash RAM and DRAM have practical advantages that have so far kept MRAM in a niche role in the market.

Non-volatile memory (NVM) or non-volatile storage is a type of computer memory that can retain stored information even after power is removed. In contrast, volatile memory needs constant power in order to retain data.

Nano-RAM is a proprietary computer memory technology from the company Nantero. It is a type of nonvolatile random-access memory based on the position of carbon nanotubes deposited on a chip-like substrate. In theory, the small size of the nanotubes allows for very high density memories. Nantero also refers to it as NRAM.

Phase-change memory is a type of non-volatile random-access memory. PRAMs exploit the unique behaviour of chalcogenide glass. In PCM, heat produced by the passage of an electric current through a heating element generally made of titanium nitride is used to either quickly heat and quench the glass, making it amorphous, or to hold it in its crystallization temperature range for some time, thereby switching it to a crystalline state. PCM also has the ability to achieve a number of distinct intermediary states, thereby having the ability to hold multiple bits in a single cell, but the difficulties in programming cells in this way has prevented these capabilities from being implemented in other technologies with the same capability.

Magnetic storage or magnetic recording is the storage of data on a magnetized medium. Magnetic storage uses different patterns of magnetisation in a magnetizable material to store data and is a form of non-volatile memory. The information is accessed using one or more read/write heads.

Density is a measure of the quantity of information bits that can be stored on a given physical space of a computer storage medium. There are three types of density: length of track, area of the surface, or in a given volume.

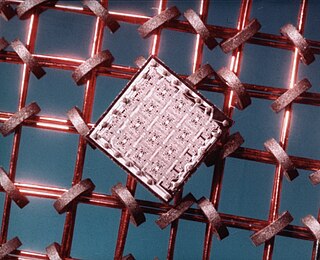

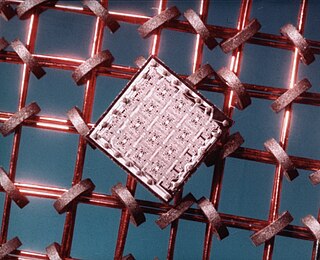

Millipede memory is a form of non-volatile computer memory. It promised a data density of more than 1 terabit per square inch, which is about the limit of the perpendicular recording hard drives. Millipede storage technology was pursued as a potential replacement for magnetic recording in hard drives and a means of reducing the physical size of the technology to that of flash media.

Ferroelectric RAM is a random-access memory similar in construction to DRAM but using a ferroelectric layer instead of a dielectric layer to achieve non-volatility. FeRAM is one of a growing number of alternative non-volatile random-access memory technologies that offer the same functionality as flash memory. An FeRAM chip contains a thin film of ferroelectric material, often lead zirconate titanate, commonly referred to as PZT. The atoms in the PZT layer change polarity in an electric field, thereby producing a power-efficient binary switch. However, the most important aspect of the PZT is that it is not affected by power disruption or magnetic interference, making FeRAM a reliable nonvolatile memory.

Spin-transfer torque (STT) is an effect in which the orientation of a magnetic layer in a magnetic tunnel junction or spin valve can be modified using a spin-polarized current.

Nanoelectronics refers to the use of nanotechnology in electronic components. The term covers a diverse set of devices and materials, with the common characteristic that they are so small that inter-atomic interactions and quantum mechanical properties need to be studied extensively. Some of these candidates include: hybrid molecular/semiconductor electronics, one-dimensional nanotubes/nanowires or advanced molecular electronics.

Universal memory refers to a computer data storage device combining the cost benefits of DRAM, the speed of SRAM, the non-volatility of flash memory along with infinite durability, and longevity. Such a device, if it ever becomes possible to develop, would have a far-reaching impact on the computer market. Some doubt that such a type of memory will ever be possible.

Random-access memory is a form of electronic computer memory that can be read and changed in any order, typically used to store working data and machine code. A random-access memory device allows data items to be read or written in almost the same amount of time irrespective of the physical location of data inside the memory, in contrast with other direct-access data storage media, where the time required to read and write data items varies significantly depending on their physical locations on the recording medium, due to mechanical limitations such as media rotation speeds and arm movement.

Everspin Technologies, Inc. is a publicly traded semiconductor company headquartered in Chandler, Arizona, United States. It develops and manufactures discrete magnetoresistive RAM or magnetoresistive random-access memory (MRAM) products, including Toggle MRAM and Spin-Transfer Torque MRAM (STT-MRAM) product families. It also licenses its technology for use in embedded MRAM (eMRAM) applications, magnetic sensor applications as well as performs backend foundry services for eMRAM.