Operation

Write

Stress to the gate, relative to channel electrodes, can be applied in the form of fixed current or bias, driving ions toward - or away from - the electrolyte/channel interface where charge transfer occurs with free carriers. Upon insertion in the channel, the ionic charge is neutralized and the atomic species intercalate or bind to the conductive host matrix, in some cases yielding strain and localized phase transformation. Such reversible processes are equivalent to anodic/cathodic reactions in battery cells or electrochromic devices. Although in ECRAM, the programming of the memory element is defined not as a change in capacity or opacity, but by a change of channel conductivity associated with atomic species being inserted or removed as a result of the stress signal.

Read

The read operation is decoupled from the write operation thanks to the presence of three electrodes, therefore limiting read disturb. A small bias is applied between the channel electrodes, with the resulting read current being proportional to the channel conductivity, hence sensing the programmed state of the device.

Speed

The programming speed of ECRAM cells is not limited by the bulk diffusion of ions. They indeed only need to cross the interface plane between the electrolyte and the channel to induce a change in conductivity. Nanosecond write pulses can indeed trigger programming. [8] Trade-offs between gate capacitance, electronic conductivity, etc., can yield settling transients, limiting the maximum read-write frequency. [9]

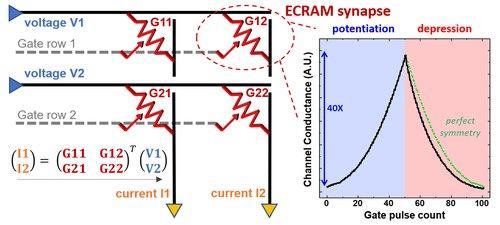

Arrays

ECRAM arrays are integrated in a pseudo-crossbar layout, the gate access line being common to all devices in a row or column. If a change in electrochemical potential, the driving force of a battery, occurs upon ionic exchange between channel and gate electrode, an open circuit potential (OCP) exists at the gate contact and will differ device to device depending on the programmed state. To prevent cross-talk between cells sharing a gate line, an access device to isolate each one is added in series with the memory element. [10] Suppressing OCP in the ECRAM design, minimizes the cell size/complexity, allowing for selector-free parallel read/programming of device arrays. [6]